# Système d'acquisition de comptages de neutrons (ou d'événements) modulaire en standard CAMAC

Francis Epaud

#### ▶ To cite this version:

Francis Epaud. Système d'acquisition de comptages de neutrons (ou d'événements) modulaire en standard CAMAC. Traitement du signal et de l'image [eess.SP]. 1984. dumas-00312806

## HAL Id: dumas-00312806 https://dumas.ccsd.cnrs.fr/dumas-00312806

Submitted on 26 Aug 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## CONSERVATOIRE NATIONAL DES ARTS ET METIERS

# CENTRE AGREE DE GRENOBLE (C.U.E.F.A)

#### MEMOIRE

présenté en vue d'obtenir

## LE DIPLOME D'INGENIEUR C.N.A.M.

en

**INFORMATIQUE**

par francis EPAUD

Les travaux relatifs au présent mémoire ont été éffectués à

l'INSTITUT LAUE -LANGEVIN de GRENOBLE Département INSTRUMENTS et METHODES dirigé par Monsieur FAUDOU

Directeur du Mémoire : Monsieur R.KLESSE

B. m. Ti 16134 313914

# CONSERVATOIRE NATIONAL DES ARTS ET METIERS

# CENTRE AGREE DE GRENOBLE (C.U.E.F.A)

MEMOIRE

présenté en vue d'obtenir

Morn line Million all TUT I AN A G NRS IN PONTINGES AN GORDING ORENOS X TOL FRANCE CEN.

LE DIPLOME D'INGENIEUR C.N.A.M.

en

**INFORMATIQUE**

par francis EPAUD

Les travaux relatifs au présent mémoire ont été éffectués à

l'INSTITUT LAUE -LANGEVIN de GRENOBLE Département INSTRUMENTS et METHODES dirigé par Monsieur FAUDOU

Directeur du Mémoire : Monsieur R.KLESSE

#### Remerciements:

J'exprime mes remerciements:

- à Monsieur le Professeur RANCHIN qui a bien voulu accepter la présidence du jury,

- à Monsieur le Professeur BOLLIET pour sa compréhension des difficultés inhérentes à ce travail,

- à Monsieur FAUDOU, responsable du Département Instruments et Méthodes, pour son autorisation de réaliser ce travail à l'ILL.

- à Monsieur KLESSE, responsable du groupe d'électroniciens au sein duquel ce travail a été réalisé,

- à Monsieur CONVERT, responsable physicien de l'expérience D20, pour le dialogue permanent qui a pu avoir lieu, et en particulier pour son aide à la compréhension des problèmes liés à la physique, et également pour ses conseils dans la rédaction du chapitre I,

- à Monsieur MUNNIER pour sa participation au jury,

- à Monsieur CHUGG, stagiaire de l'Université d'Oxford pour son aide,

- à Mademoiselle KILLIAN, qui a bien voulu frapper le présent mémoire,

- à tous mes amis pour leur aide et leur encouragement.

### SOMMAIRE

| ٠. |                                                                                                                                 | Page           |

|----|---------------------------------------------------------------------------------------------------------------------------------|----------------|

| IN | TRODUCTION                                                                                                                      | 11             |

| ı. | NEUTRON, NEUTRONIQUE, CAS PARTICULIER DE L'INSTRUMENT D20,<br>SYSTEMES D'ACQUISITION DES COMPTAGES DE NEUTRONS                  | 13             |

|    | I.1. Les neutrons thermiques                                                                                                    | 13             |

|    | I.l.l. Caractéristiques                                                                                                         | 13<br>15       |

|    | I.2. Les grandes familles d'appareils de diffraction neutronique                                                                | . 16           |

|    | I.2.1. Les diffractomètres                                                                                                      |                |

|    | <ol> <li>Diffractomètres 4 cercles pour monocristaux</li> <li>Diffractomètres à 2 axes (étude des poudres et liquides</li></ol> | 17             |

|    | I.2.2. Les appareils de diffusion inélastique                                                                                   | 10             |

|    | 1. Appareils de diffusion à 3 axes                                                                                              | . 18           |

|    | I.3. Cas particulier de l'instrument D20                                                                                        | . 19           |

|    | I.4. Systèmes d'acquisition des comptages de neutrons                                                                           | . 20           |

|    | I.4.1. Monodétecteur et chaîne d'acquisition                                                                                    | 20<br>20<br>21 |

| ΙI | L. DESCRIPTION DES BUS UTILISES                                                                                                 | . 24           |

|    | II.l. Description du bus CAMAC                                                                                                  |                |

|    | II.2. Description du bus I2C                                                                                                    | . 26           |

|    | II.2.1. Fonctionnement                                                                                                          | . 30           |

| ΙI | II. DESCRIPTION MATERIELLE                                                                                                      | . 36           |

|    | III.l. Extrait du cahier des charges                                                                                            | . 36           |

|    | III.2. Description des modules                                                                                                  | • 37           |

|    | III.3. Description des circuits utilisés                                                                                        | . 37           |

|    | III.3.1. Compteur/Temporisateur Am 9513                                                                                         | 37             |

|                      |                                                                                                                                                                 | Page                                 |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

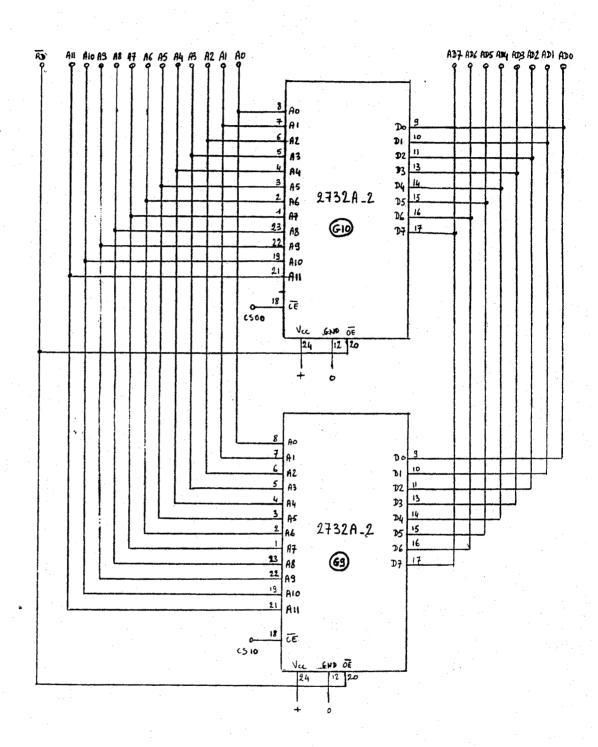

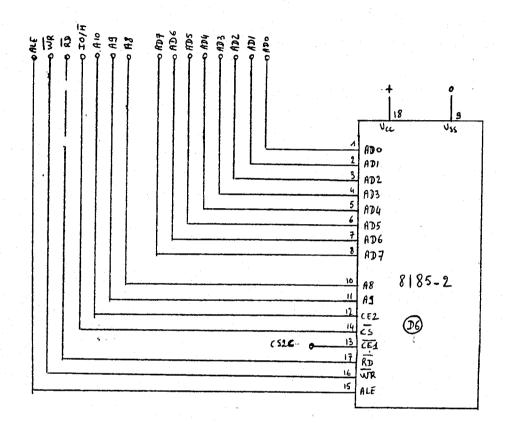

| III.3.4.             | Circuits mémoires                                                                                                                                               | 41                                   |

|                      | 1. EPROM 2732A.2                                                                                                                                                | 41<br>42                             |

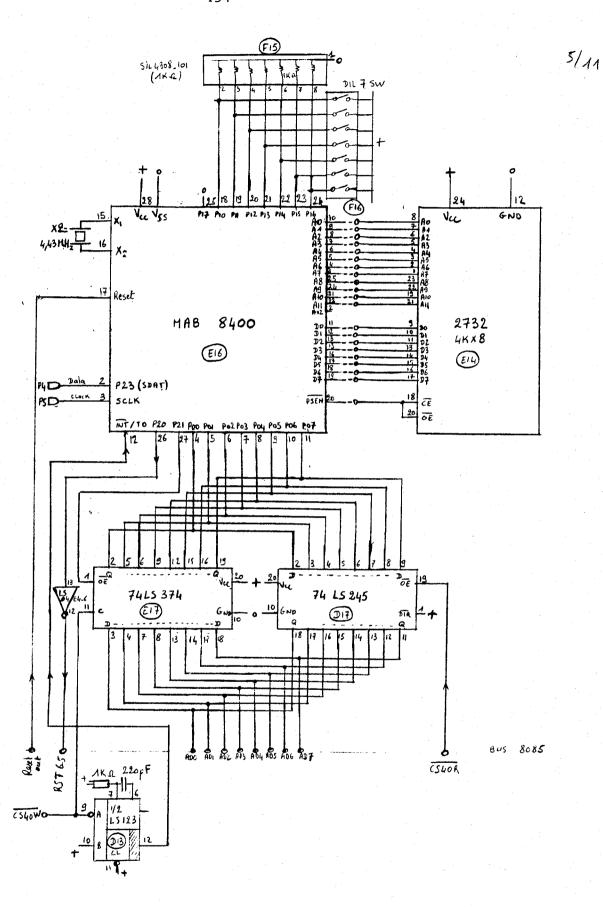

| III.3.5.             | Micro ordinateur MAB 8400                                                                                                                                       | 42                                   |

|                      | ription de l'expérience D20                                                                                                                                     |                                      |

| III.4.1.             | Généralités                                                                                                                                                     | 43                                   |

|                      | 1. Multidétecteur et électronique analogique associée .<br>2. Système d'acquisition des données                                                                 | 43                                   |

| III.4.3.             | Fonctionnement général                                                                                                                                          | . 40                                 |

| III.5. Modu          | le compteur 32 voies                                                                                                                                            | . 52                                 |

| III.5.1.<br>III.5.2. | Organisation du module                                                                                                                                          | . 55                                 |

|                      | 1. Comptage                                                                                                                                                     | . 57<br>. 59                         |

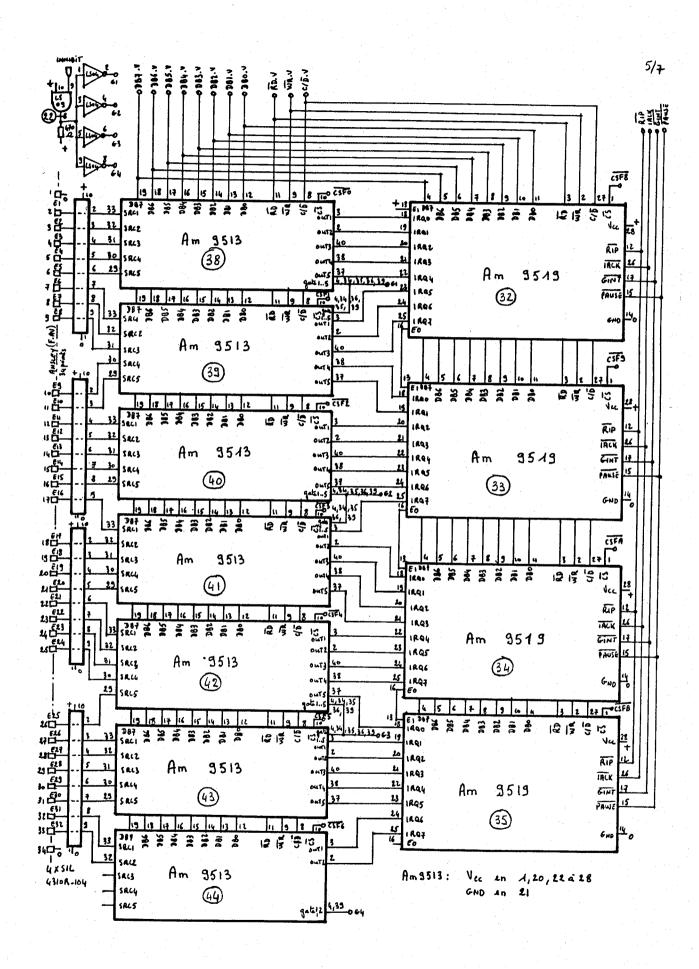

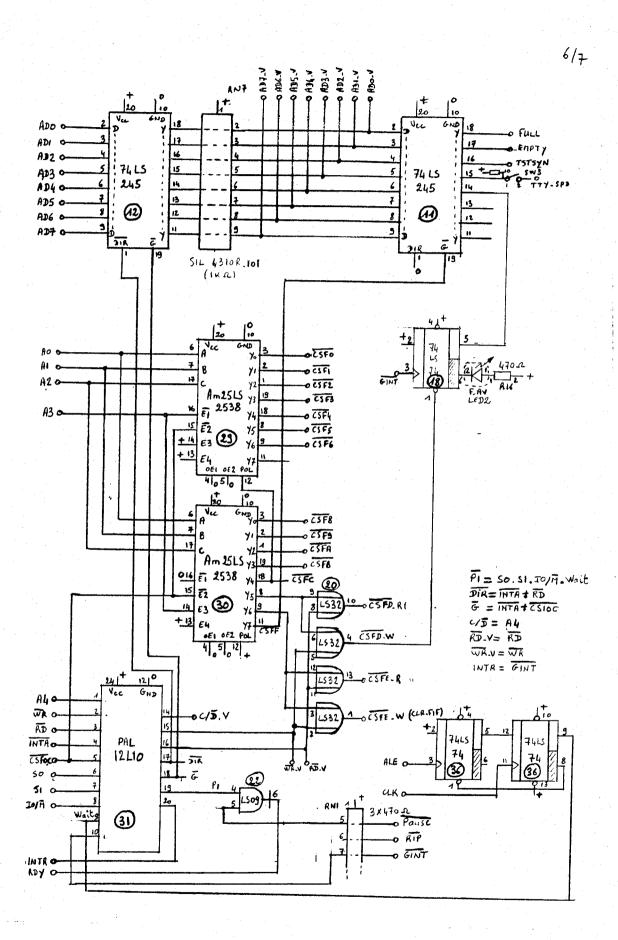

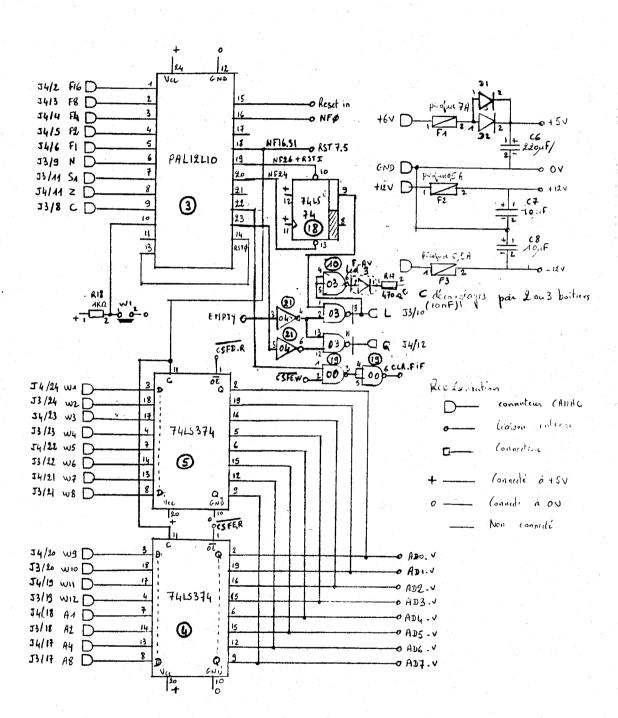

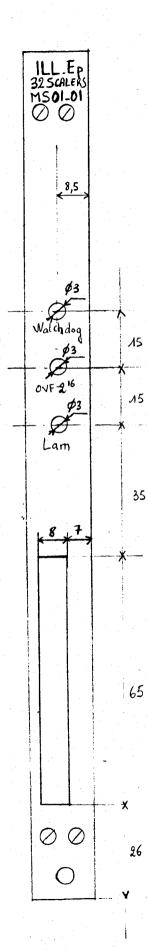

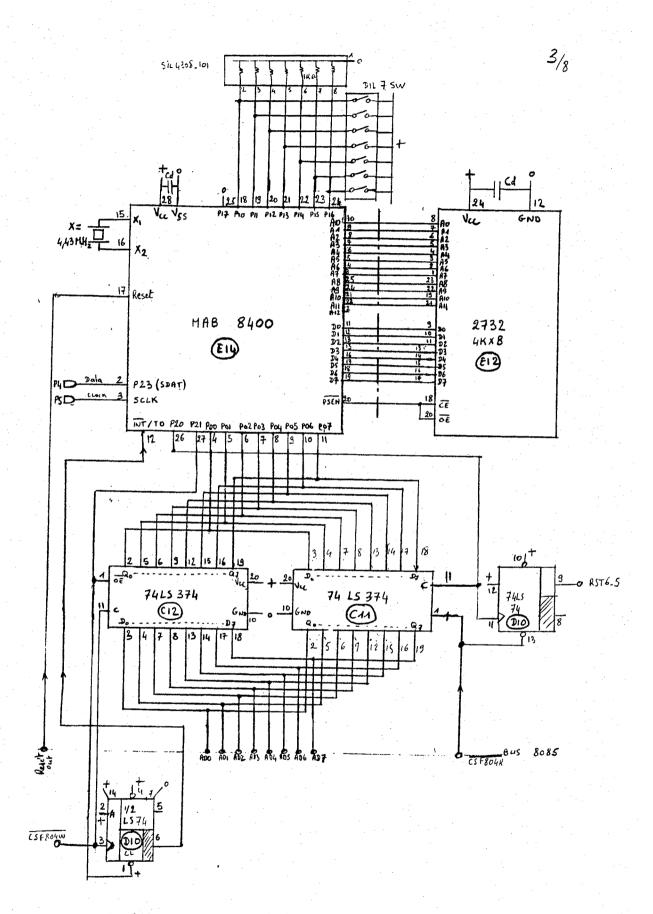

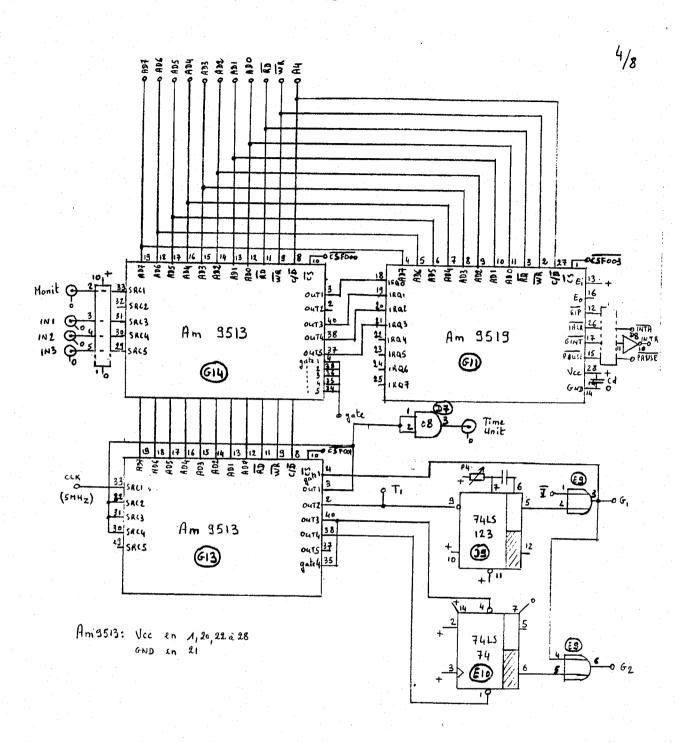

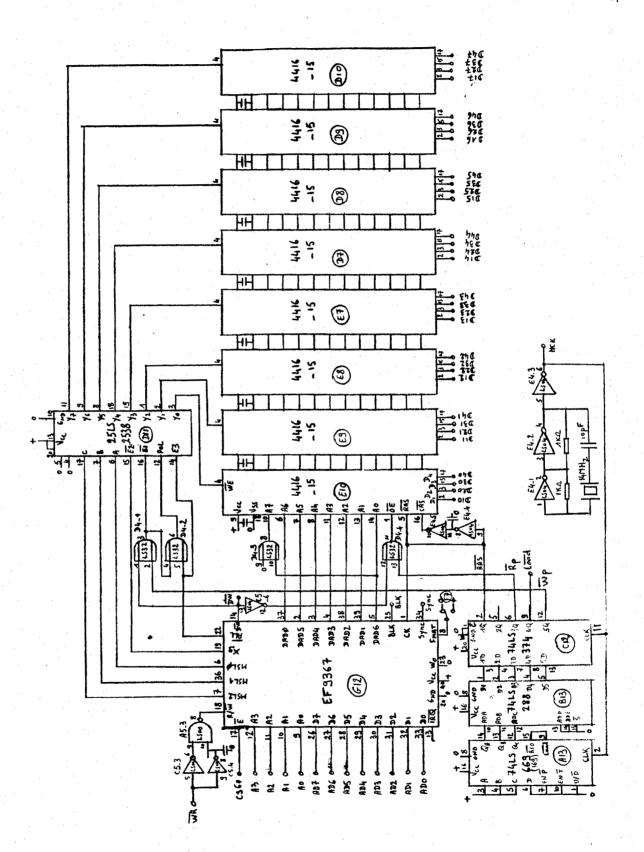

| III.5.3.             | Schémas                                                                                                                                                         | . 60                                 |

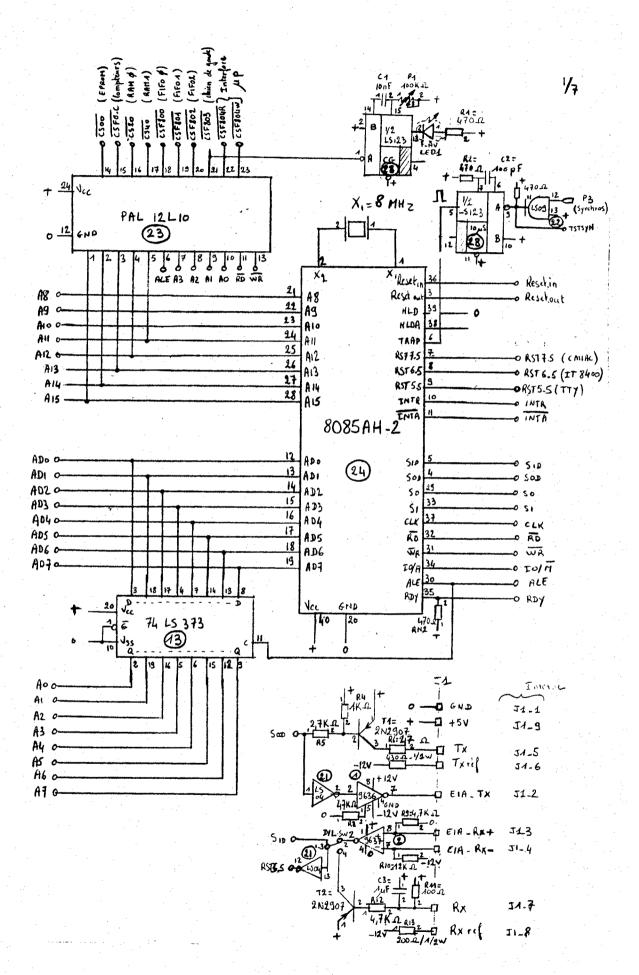

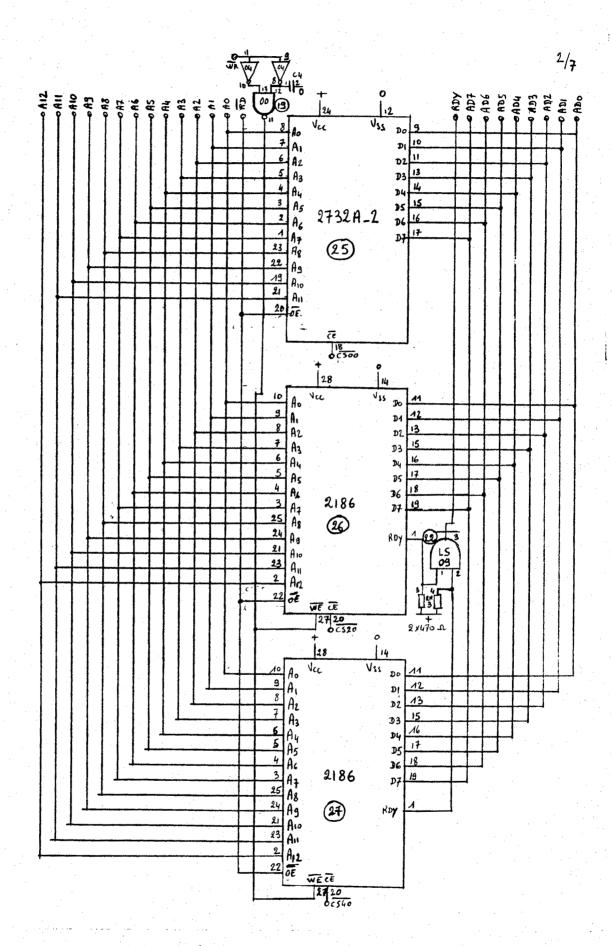

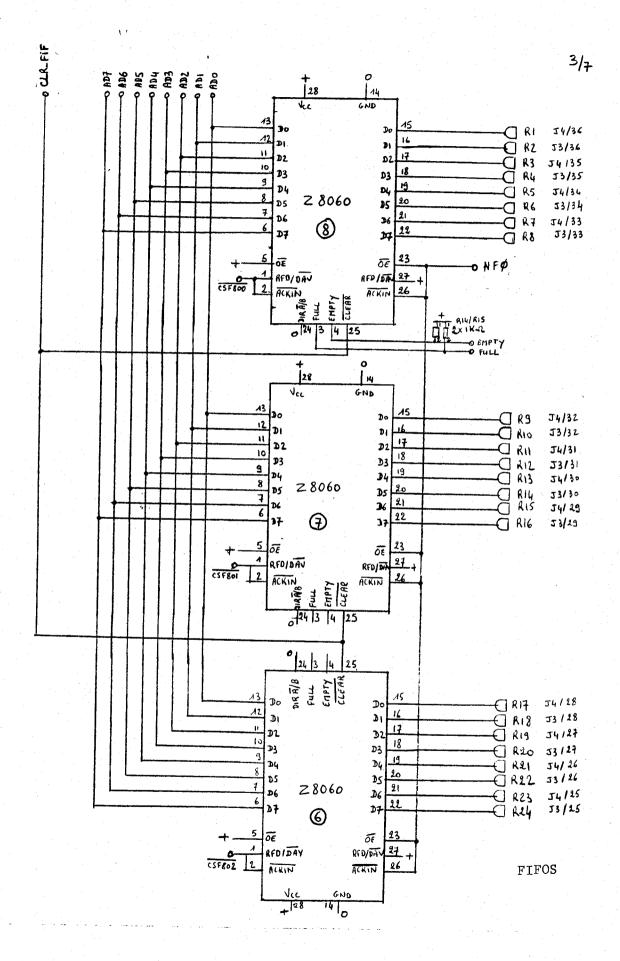

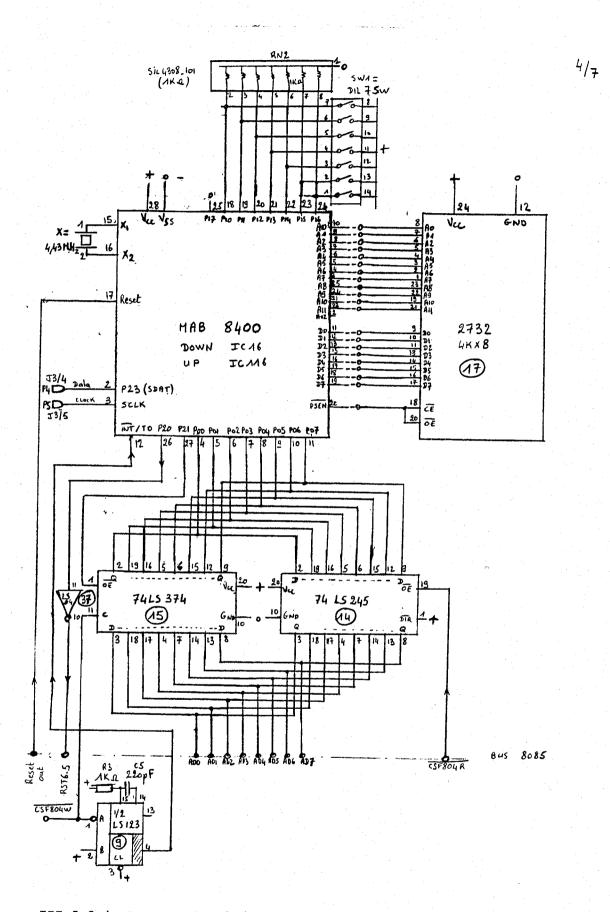

| •                    | 1. CPU + Interface TTY                                                                                                                                          | . 62<br>. 63<br>. 64<br>. 65<br>. 66 |

|                      | ule synchronisation                                                                                                                                             |                                      |

| III.6.1.<br>III.6.2. | Organisation du module                                                                                                                                          | . 69<br>. 71                         |

|                      | 1. Comptage                                                                                                                                                     | . 72<br>. 76<br>. 79                 |

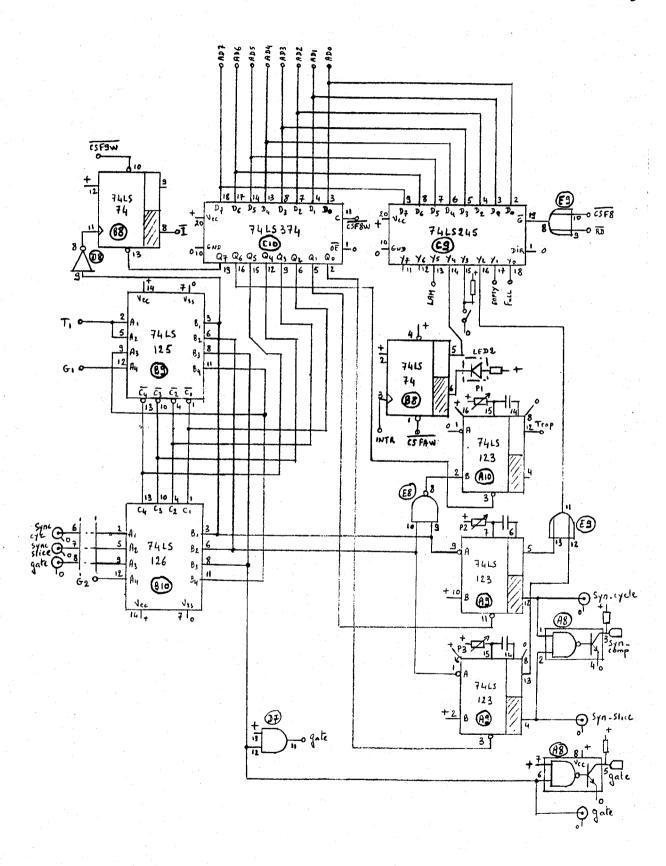

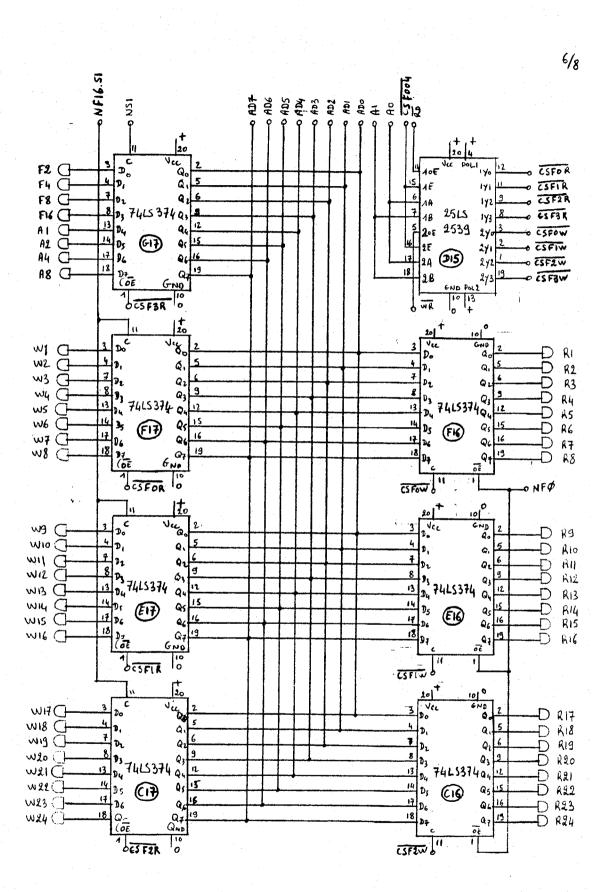

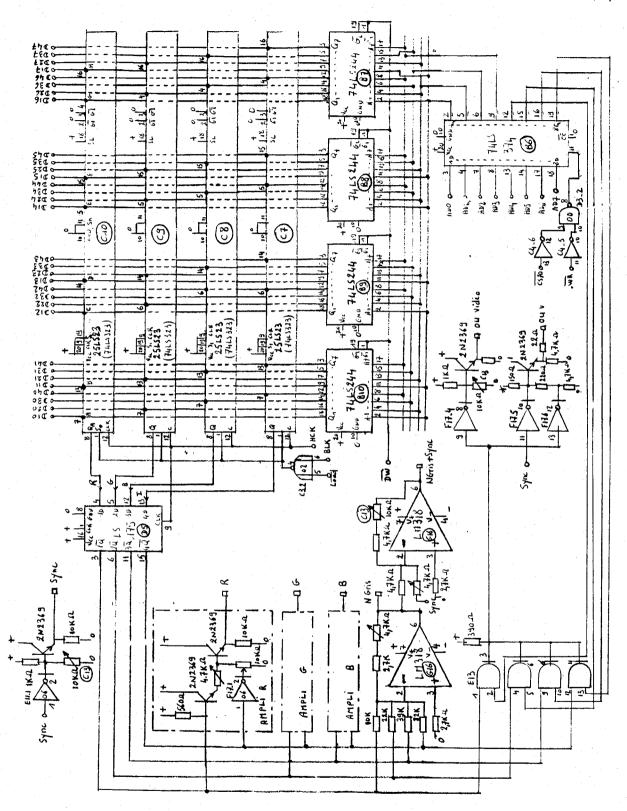

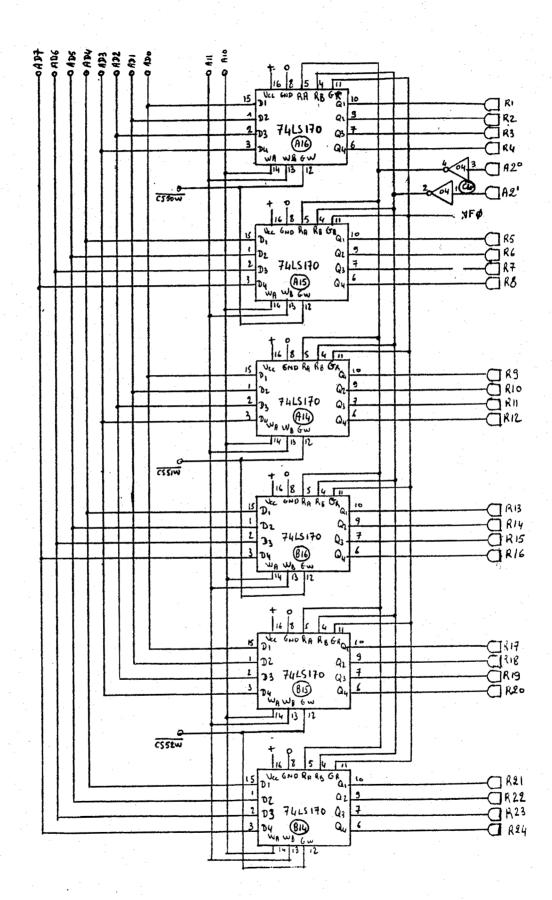

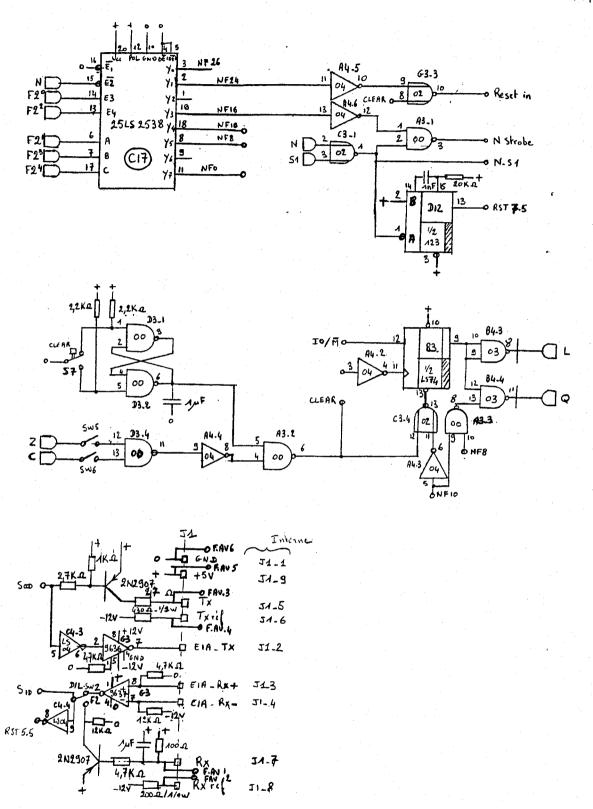

| III.6.3.             | Schémas                                                                                                                                                         |                                      |

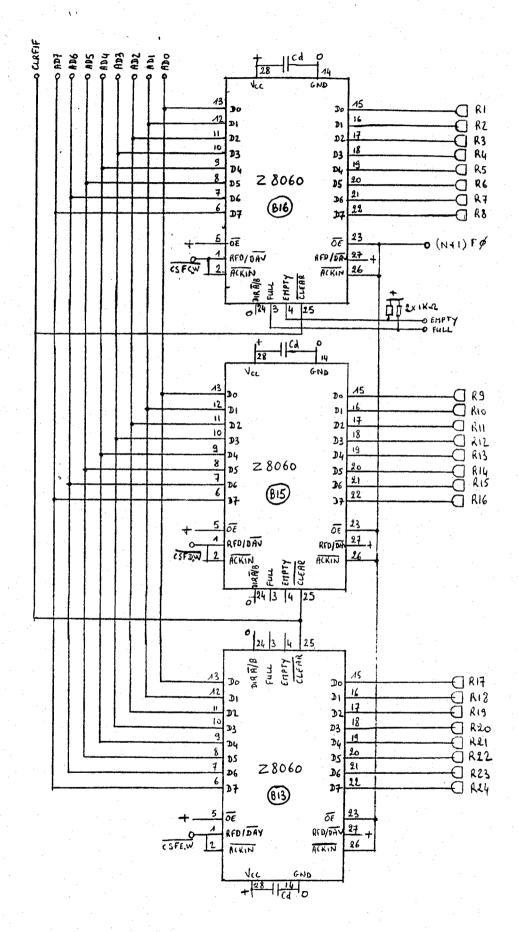

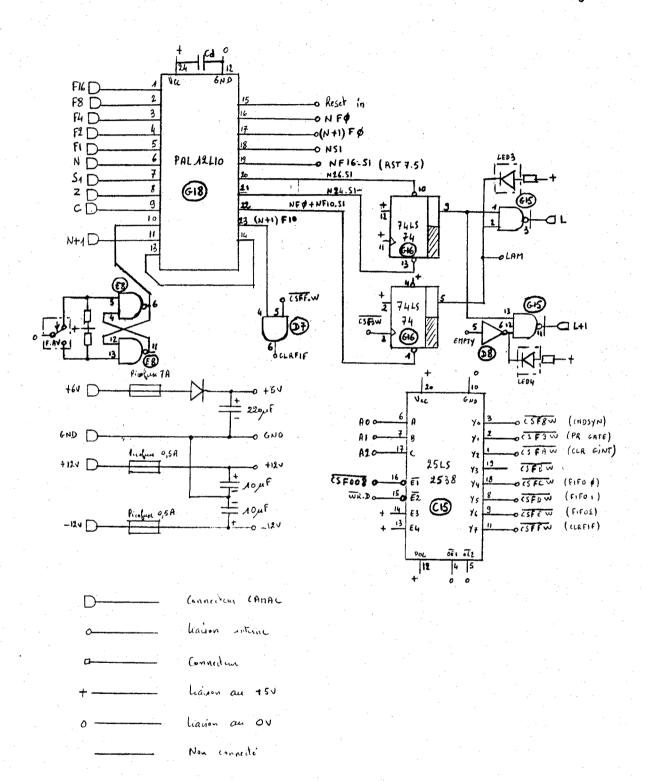

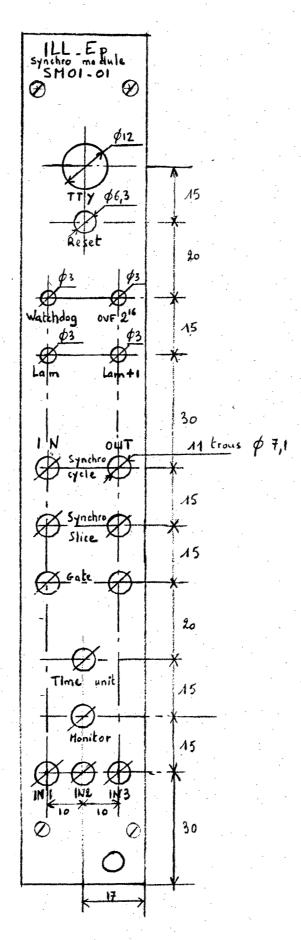

|                      | 1. CPU + Interface TTY 2. Mémoires 3. Processeur d'E/S + Interface 4. Temporisateur et compteur 5. Multiplexeur de synchronisations 6. Interface CAMAC 7. Fifos | 82<br>83<br>84<br>85<br>86           |

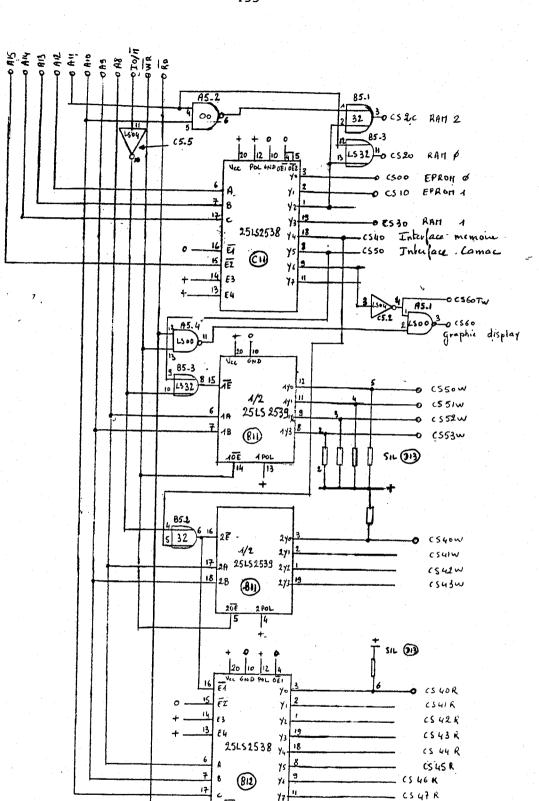

|                      | 8. Décodage                                                                                                                                                     | • •                                  |

|     |                                                                                                                                                                                                                                                                                                              | rage                                                        |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| ۲V. | LOGICIEL                                                                                                                                                                                                                                                                                                     |                                                             |

|     | IV.1. Développement du logiciel                                                                                                                                                                                                                                                                              | 89                                                          |

|     | IV.1.1. Programmation modulaire                                                                                                                                                                                                                                                                              | 91                                                          |

|     | nisation                                                                                                                                                                                                                                                                                                     |                                                             |

|     | IV.2. Bibiothèque mathématique                                                                                                                                                                                                                                                                               | 93                                                          |

|     | IV.2.1. MCMP IV.2.2. MADD IV.2.3. MDECAL IV.2.4. COPBUF IV.2.5. RAZBUF IV.2.6. MULT96                                                                                                                                                                                                                        | 94<br>94<br>95<br>96                                        |

|     | IV.3. Bibliothèque moniteur télétype                                                                                                                                                                                                                                                                         | 96                                                          |

|     | IV.3.1. INITTY IV.3.2. READ IV.3.3. CI IV.3.4. WRITE IV.3.5. CRLF IV.3.6. WRITLN IV.3.7. CO IV.3.8. DELAY                                                                                                                                                                                                    | 98<br>99<br>100<br>100<br>100                               |

|     | IV.4. Logiciel de la carte compteur 32 voies                                                                                                                                                                                                                                                                 | . 101                                                       |

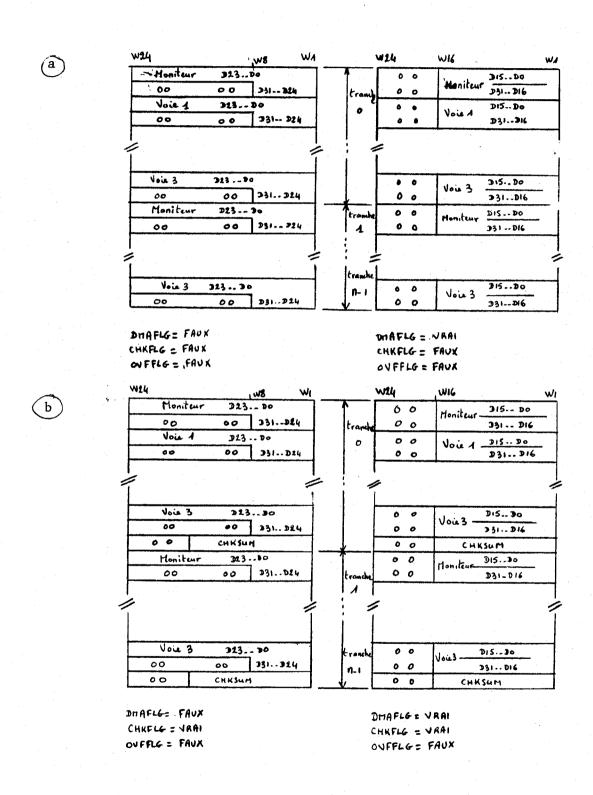

|     | IV.4.1. Organisation des données IV.4.2. Organisation des transferts en sortie IV.4.3. Organisation des transferts interprocesseur IV.4.4. Algorithmes  1. Fonctionnement des sémaphores et masques 2. Sémaphores, pointeurs et vecteurs utilisés 3. SCALER 4. CAMAC et CMCANA 5. NXTSPC et MLTADD 6. FIFOWR | . 103<br>. 107<br>. 110<br>. 111<br>. 112<br>. 112<br>. 114 |

|     | 7. VECTX, INCREM, DEBORD 8. NEXTSP 9. FIFRQT 10. RECOIT 11. VISAV 12. LIRE 13. TSTMEM et CMPMEM 14. PROCES, ENVOI et RECOIT                                                                                                                                                                                  | . 116<br>. 117<br>. 117<br>. 117<br>. 118<br>. 118          |

|     | IV.4.5. Activité processeur                                                                                                                                                                                                                                                                                  |                                                             |

|     | IV.5. Logiciel de la carte synchronisation                                                                                                                                                                                                                                                                   |                                                             |

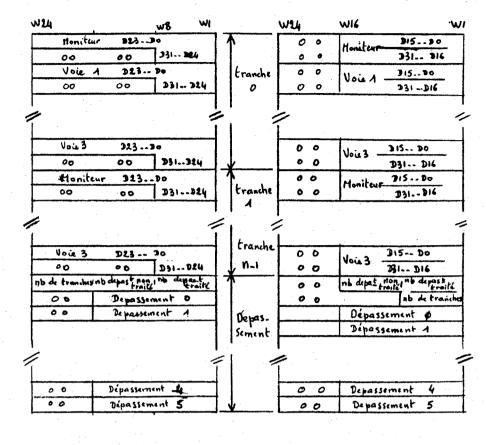

|     | IV.5.1. Organisation des données                                                                                                                                                                                                                                                                             | . 122<br>. 125                                              |

|    |             |                                                    |               | Page         |

|----|-------------|----------------------------------------------------|---------------|--------------|

|    |             |                                                    |               |              |

|    | IV.5.       | 3. Algorithmes                                     |               | . 125        |

|    |             | 1. Sémaphores, pointeurs et vecteurs utilisés .    |               |              |

|    |             | 2. SYNCRO                                          |               | . 126        |

|    |             | 3. CAMAC et CMCANA                                 |               | . 127        |

|    |             | 4. NXTSPC et LECT                                  |               | . 129        |

|    |             | 5. FIFOWR                                          |               | . 130        |

|    |             | 6. VECTO, VECTX, INCREM, DEBORD                    |               | . 131        |

|    | •           | 7. NEXTSP                                          |               | . 132        |

|    |             | 8. FIFROT                                          |               | . 132        |

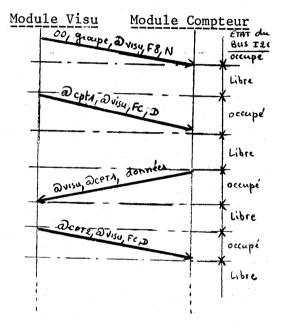

|    |             | 9. ENVOI. RECOIT, TRI2C                            |               | . 132        |

|    |             | 10. LOADTM, LOADCP                                 |               | . 133        |

|    |             | 11. TSTMEM, CMPMEM                                 | • • • • • •   | . 134        |

|    |             | 12. PROCES, RECOIT                                 | • • • • • •   | . 135        |

|    |             |                                                    | •             | 126          |

| ٧. |             | SUALISATION                                        |               |              |

|    | V.1. Desc   | ription du processeur graphique EF9367             | • • • • • •   | . 136        |

|    | 77 1 1      | Généralités                                        |               | . 136        |

|    | V.I.I.      | Registres internes aux GDP                         |               | . 137        |

|    | V • 1 • 2 • |                                                    |               |              |

|    |             | 1. X et Y                                          | • • • • • •   | 137          |

|    |             | 2. Delta X et Delta Y                              | • • • • • •   | 137          |

|    |             | 3. CSIZE                                           | • • • • • • • | 137          |

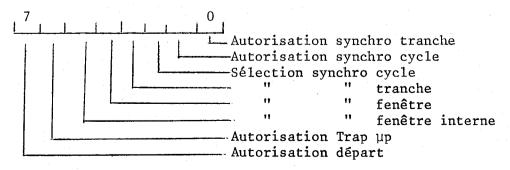

|    |             | 5. CTRL 2                                          |               | . 138        |

|    |             | 6. Commande                                        |               | . 138        |

|    |             | 7. Etat                                            |               | . 138        |

|    |             | 8. XLP et YLP                                      |               | . 139        |

|    | 1 0         |                                                    |               |              |

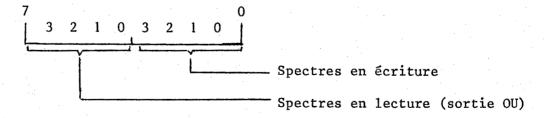

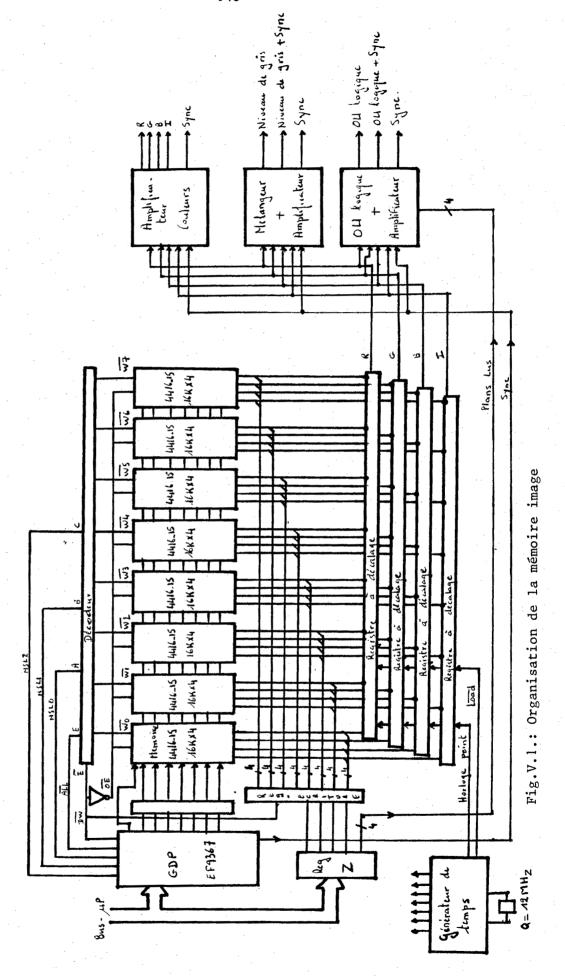

|    | , V.1.3.    | Organisation de la mémoire image                   | , <b></b>     | 1.60         |

|    | V.2. Orga   | anisation du module                                |               | . 142        |

|    |             | ctionnement                                        |               |              |

|    | V.3.1.      | Interface CAMAC                                    |               | . 145        |

|    |             | 1. Fonctions CAMAC                                 |               | . 146        |

|    |             | 2. Accès aux paramètres du programme de visualisat | tion          | . 146        |

|    |             | 3. Accès aux données du système d'acquisition      |               | . 14/        |

|    |             | 4. Accès au GDP                                    |               | 147          |

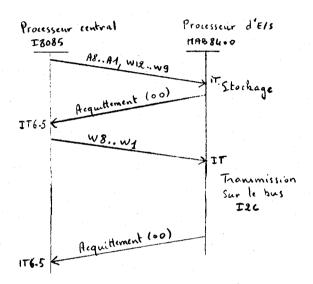

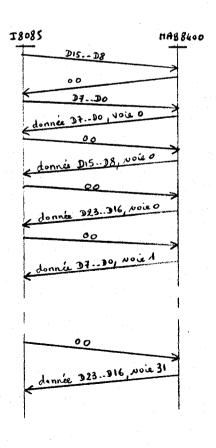

|    | 17 2 2      | Interface uprocesseur 8085 / ordinateur MAB8400 .  |               |              |

|    | V.J.Z.      | Ecriture dans le GDP                               |               | 149          |

|    |             |                                                    |               |              |

|    | V.4. Sch    | émas                                               |               | 149          |

|    | V / 1       | CPU                                                | • • • • • •   | . 150        |

|    | V 4 2       | Mémoires EPROM                                     |               | . 151        |

|    | 7.4.3       | Mémoires RAM + Entrée CAMAC                        |               | . 152        |

|    | V. 4. 4.    | Mémoires RAM 1 K octets                            |               | . 153        |

|    | V. 4.5.     | Processeur d'E/S + Interface                       |               | 154          |

|    | V. 4.6      | Décodage d'adresse                                 |               | 155          |

|    | V.4.7.      | CDP et mémoire image                               |               | •• 130       |

|    | V. 4. 8.    | Mélangeur vidéo                                    |               | 157          |

|    | 77 / Q      | Sortie CAMAC                                       |               | 158          |

|    | V.4.10.     | Interface TTY, décodeur de fonctions CAMAC         | • • • • • • • | . 159<br>160 |

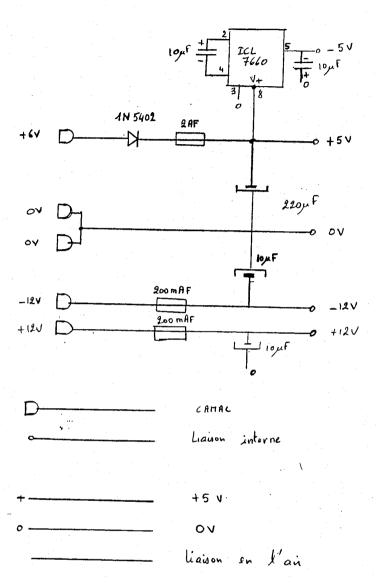

|    | V.4.11.     | Alimentation + connexions                          | • • • • • •   | 160<br>161   |

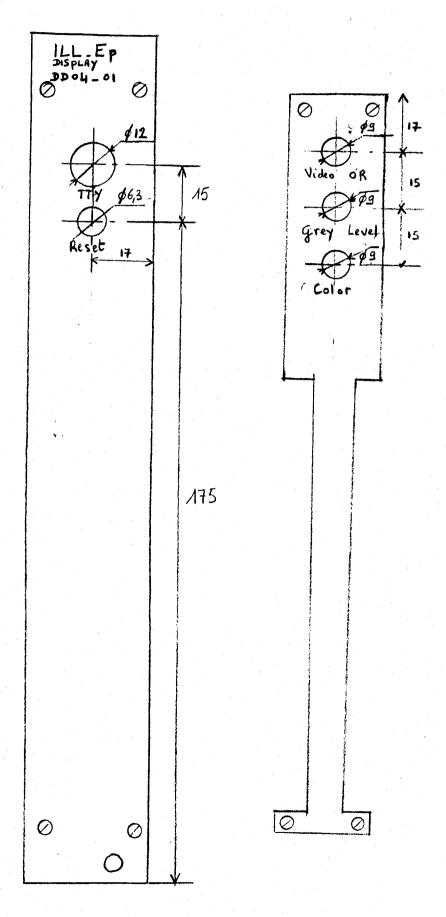

|    | V.4.12.     | Faces avant et arrière                             | • • • • • • • | •• • • •     |

|      | r en                                                                | age                                    |

|------|---------------------------------------------------------------------------------------------------------|----------------------------------------|

|      | V.5. Logiciel                                                                                           | 162                                    |

|      | V.5.1. Généralités                                                                                      | 162<br>163<br>165                      |

|      | 1. SPECTrum 2. ISOmétrique (et LISO) 3. CONTur 4. LIST 5. Gestion du curseur 6. HELP 7. EXIT 8. LO.S/ST | 165<br>166<br>167<br>168<br>169<br>169 |

| VI.  | RESULTATS                                                                                               | 170                                    |

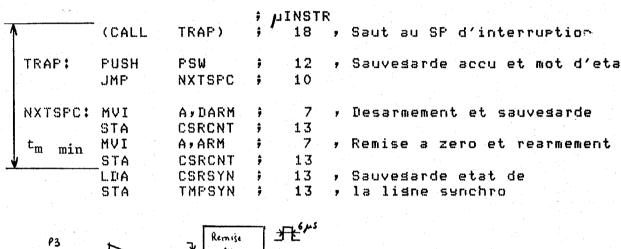

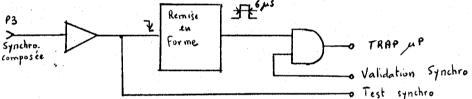

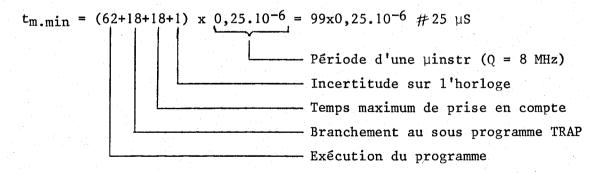

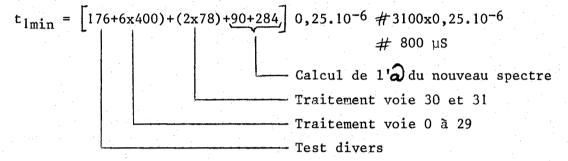

|      | VI.1. Amélioration de t <sub>m</sub>                                                                    | 171<br>172                             |

| CON  | LUSION                                                                                                  | 176                                    |

| BIBI | LOGRAPHIE                                                                                               | 182                                    |

| ANNI | KES                                                                                                     | 177                                    |

| B :  | Macro-instructions pour le micro-ordinateur MAB8400                                                     | 177<br>178<br>179                      |

| E    | Ecriture dans le CDP                                                                                    | 181                                    |

#### LISTE DES FIGURES

|        |                                                                                                     | _    |

|--------|-----------------------------------------------------------------------------------------------------|------|

|        |                                                                                                     | Page |

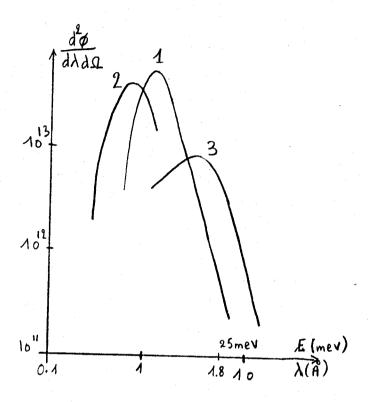

| I.1.   | Spectres du flux de neutrons thermiques                                                             | 14   |

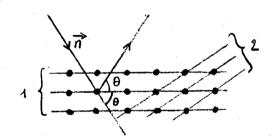

| I.2.   | Réflexion de Bragg sur une famille de plan atomique d'un cristal                                    | 15   |

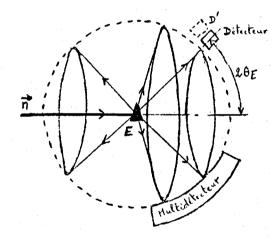

| 1.3.   | Principe d'un diffractomètre à 4 cercles                                                            | 16   |

| I.4.   | Diffractomètre à 2 axes avec cônes de diffractions                                                  | 17   |

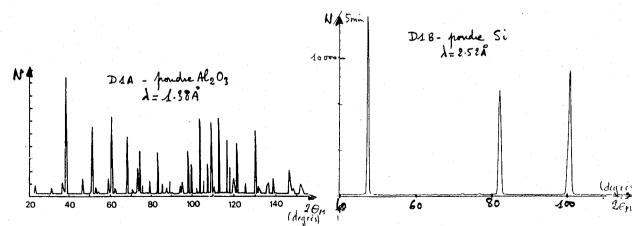

| 1.5.   | Diagramme de 2 poudres typiques                                                                     | 17   |

| 1.6.   | Principe d'un appareil de diffusion à 3 axes                                                        |      |

| I.7.   | Principe d'un appareil de diffusion à temps de vol                                                  | 18   |

| 1.8.   | Principe d'un appareil avec monodétecteur et chaîne d'acquisition unique                            | 20   |

| 1.9.   | Principe d'un appareil avec multidétecteur et mémoire externe.                                      | 21   |

|        | Principe d'une acquisition de comptage en incrémentation directe en mémoire centrale du calculateur | 21   |

| I.11.  | Principe d'une acquisition avec une chaîne de comptage par détecteur ou fils                        |      |

| I.12.  | Principe d'une acquisition de comptage cinétique                                                    |      |

| 1.13.  | Interprétation graphique de mesure cinétique                                                        | . 23 |

|        |                                                                                                     |      |

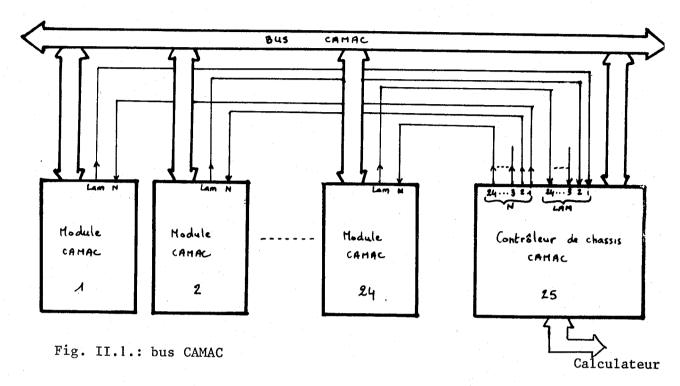

| II.1.  | Bus CAMAC                                                                                           |      |

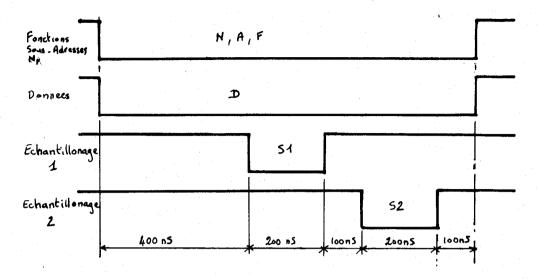

| II.2.  | Diagramme des temps d'une fonction CAMAC                                                            |      |

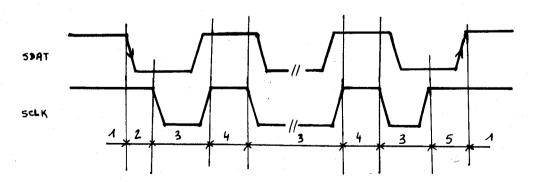

| 11.3.  | Différentes phases d'un échange sur le bus I2C                                                      |      |

| II.4.  | Synchronisation de deux noeuds du réseau                                                            |      |

| 11.5.  | Arbitrage entre deux maîtres demandant le bus                                                       |      |

| 11.6.  | Synchronisation des horloges                                                                        |      |

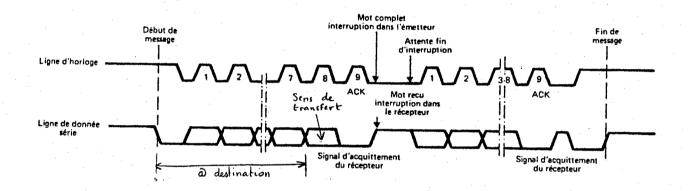

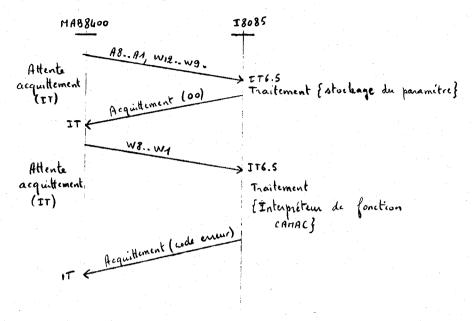

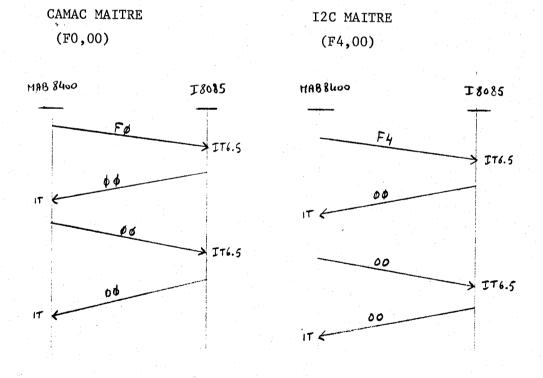

| II.7.  | Travail en mode acquittement                                                                        |      |

| 11.8.  | Réseau de modules CAMAC                                                                             |      |

| 11.9.  | Taux de transfert en fonction du nombre d'octets transmis                                           | . 33 |

| III.1. | Architecture interne du circuit compteur Am 9513                                                    | 38   |

| III.2. | Architecture d'un groupe de compteur                                                                | ~ ~  |

| III.3. | Diagramme de temps d'une reconnaissance d'interruption                                              |      |

| III.4. | Multidétecteur et électronique analogique associée                                                  |      |

| III.5. | Synoptique D20                                                                                      |      |

| III.6. | Acquisition avec tranches de temps égales                                                           |      |

| III.7. | • • •                                                                                               |      |

|         |                                                                | rage |

|---------|----------------------------------------------------------------|------|

| 111.8.  | Acquisition avec fenêtrage et récomposition du spectre         | 47   |

| 111.9.  | Génération des temps                                           | 48   |

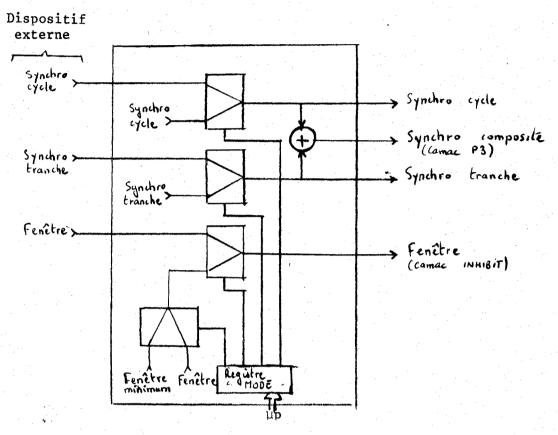

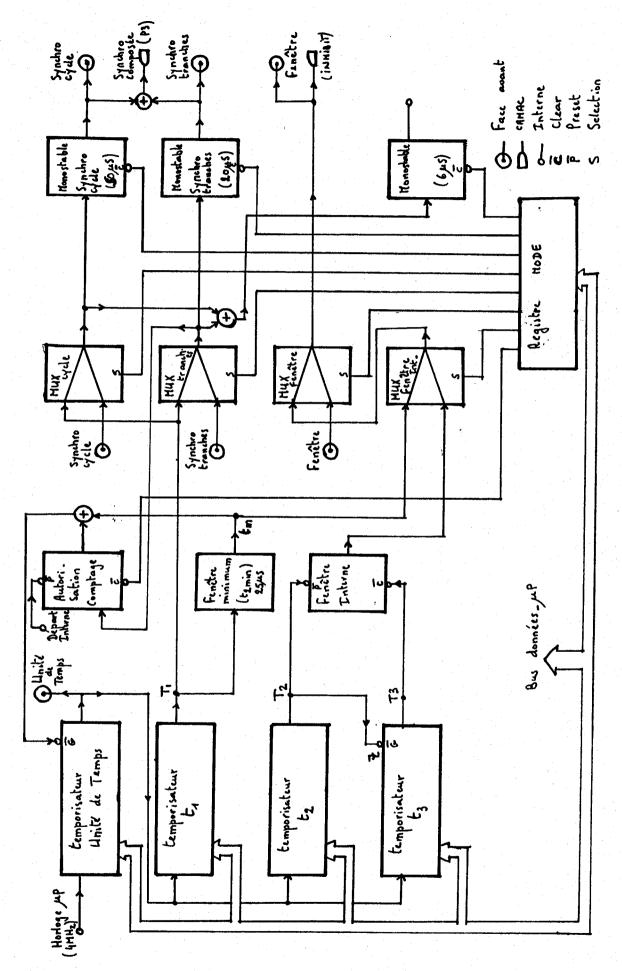

| 111.10. | Multiplexeur de synchronisations                               | 49   |

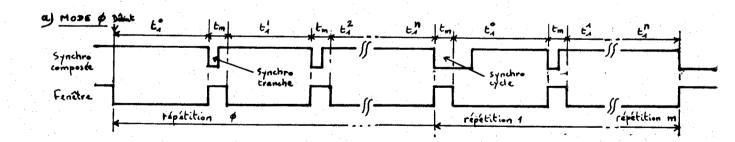

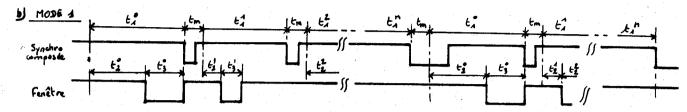

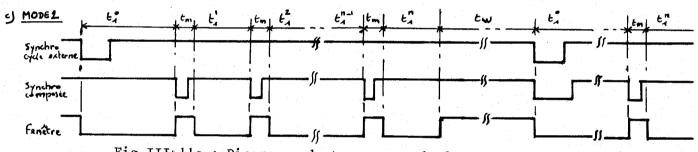

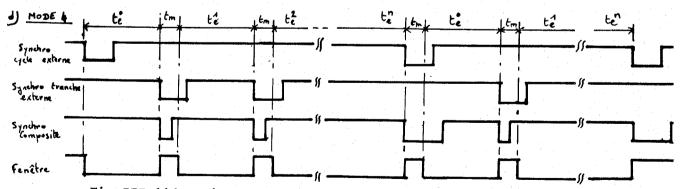

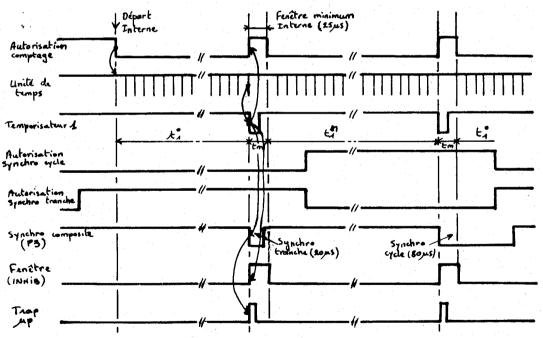

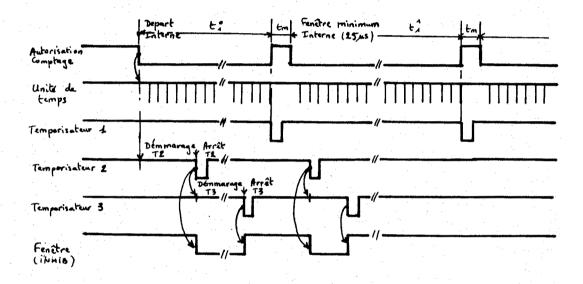

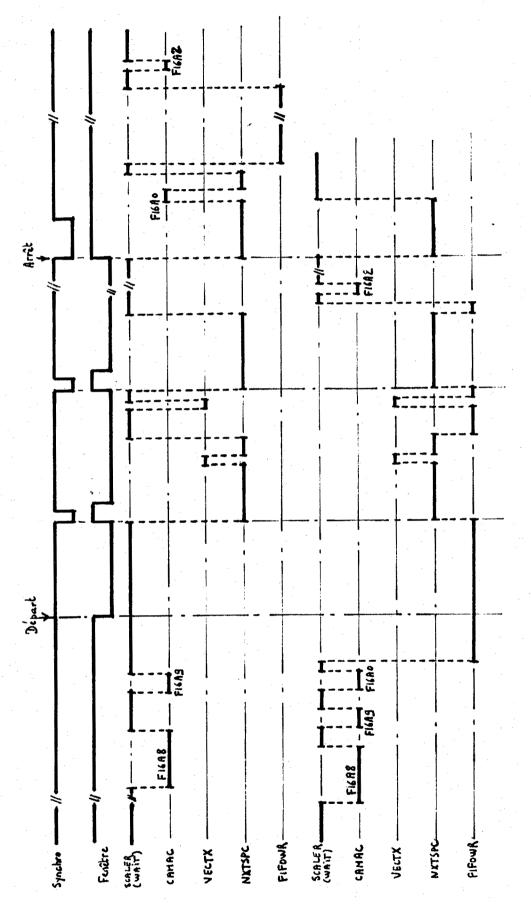

| III.11. | Diagramme de temps dans les différents modes de fonctionnement | 49   |

| III.12. | Câblage du signal de synchronisation composée                  | 51   |

| III.13. | Synoptique du module compteur 32 voies                         | 53   |

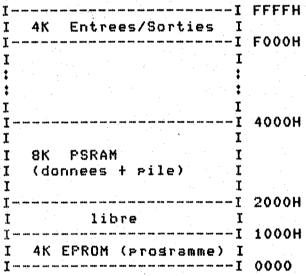

| III.14. | Zones mémoires du modules compteur 32 voies                    | 54   |

| III.15. | Caractéristiques des impulsions d'entrées                      | 56   |

| III.16. | Synoptique de la sortie CAMAC                                  | 59   |

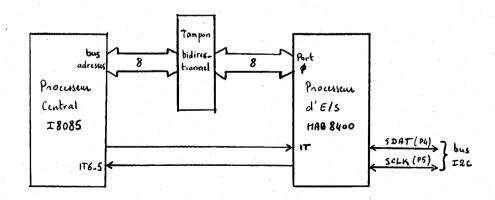

| 111.17. | Interface processeur central/processeur d'E/S                  | 59   |

| III.18. | Zones mémoires du module synchronisation                       | 69   |

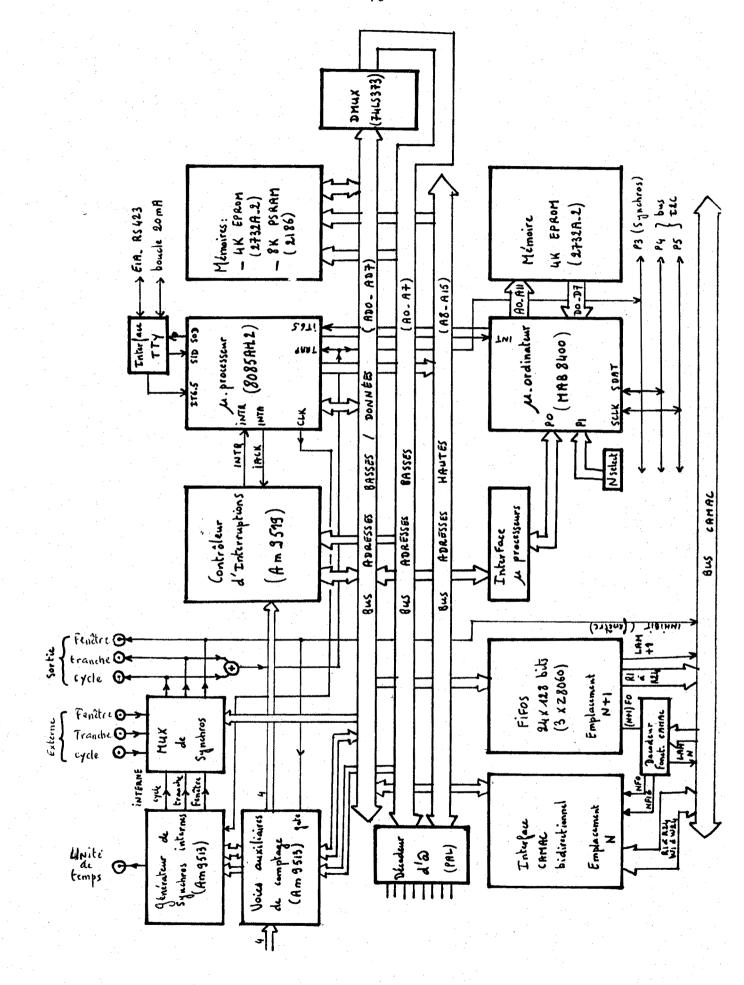

| III.19. | Synoptique du module synchronisation                           | 70   |

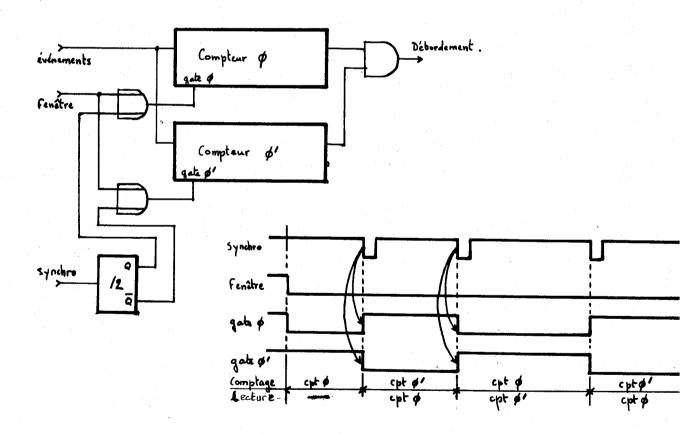

| III.20. | Synoptique du multiplexeur de synchronisation                  | 73   |

| III.21. | Diagramme des temps en mode $\emptyset$                        | 74   |

| III.22. | Diagramme des temps en mode $l$                                | 75   |

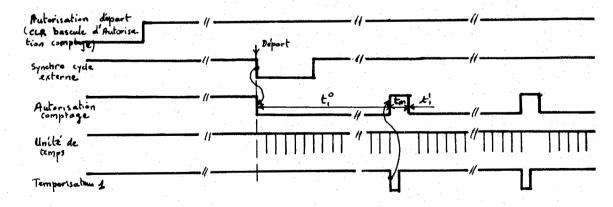

| III.23. | Synchronisation par un signal cycle externe                    | 75   |

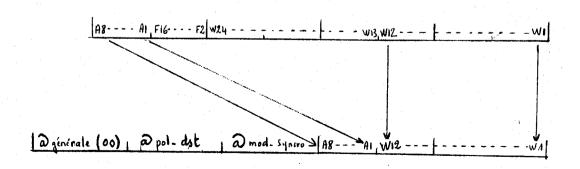

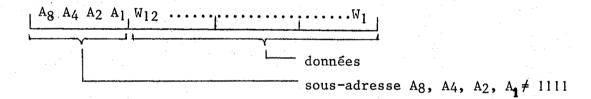

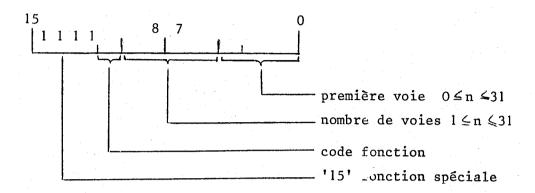

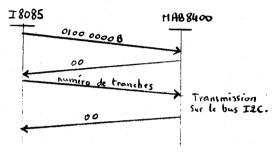

| III.24. | Format des instructions envoyées sur le bus I2C                | 76   |

| III.25. | Fonctionnement en mode manuel                                  | .79  |

| r ·     |                                                                |      |

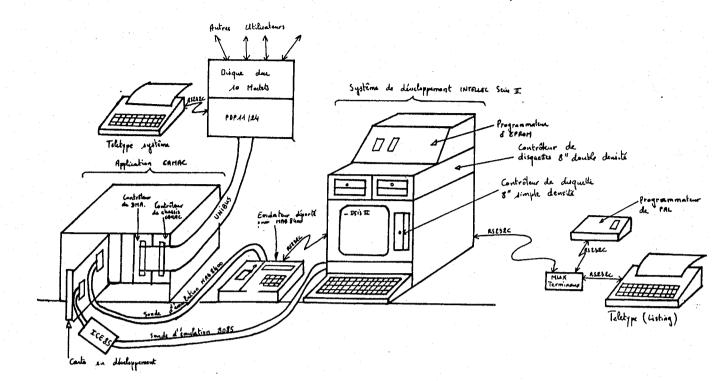

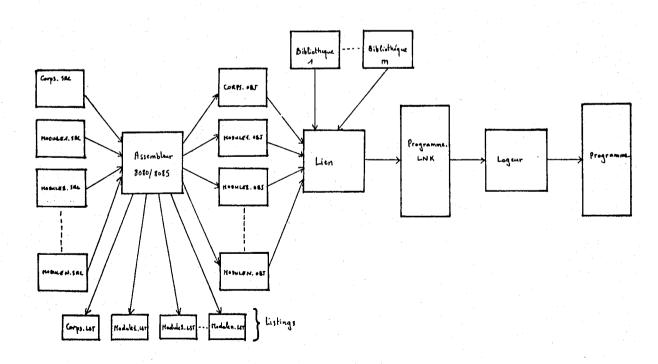

| IV.1.   | Système de développement                                       | . 90 |

| IV.2.   | Programmation modulaire                                        | 90   |

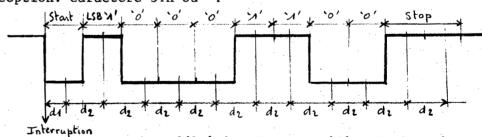

| IV.3.   | Transmission série des caractères                              | 97   |

| IV.4.   | Fonctionnement en DMA                                          | 104  |

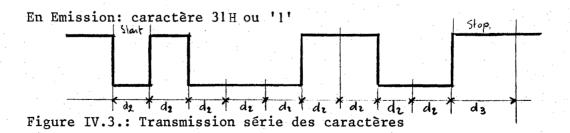

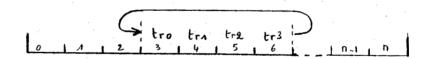

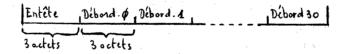

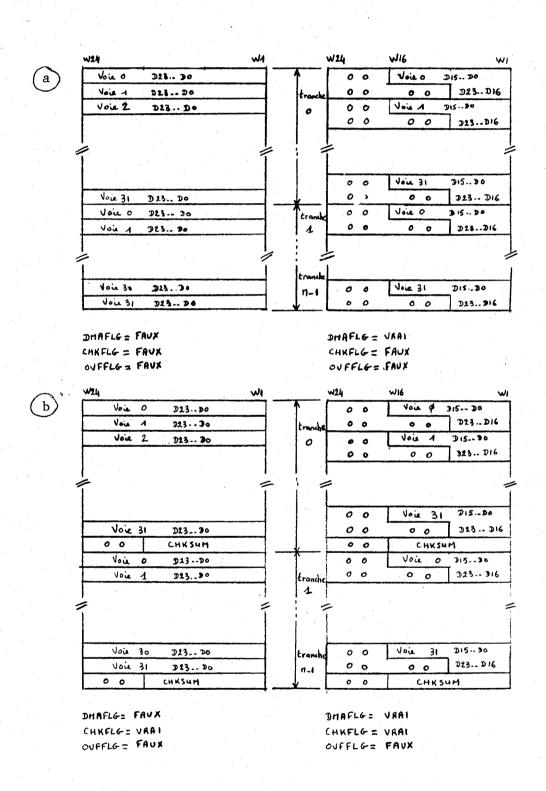

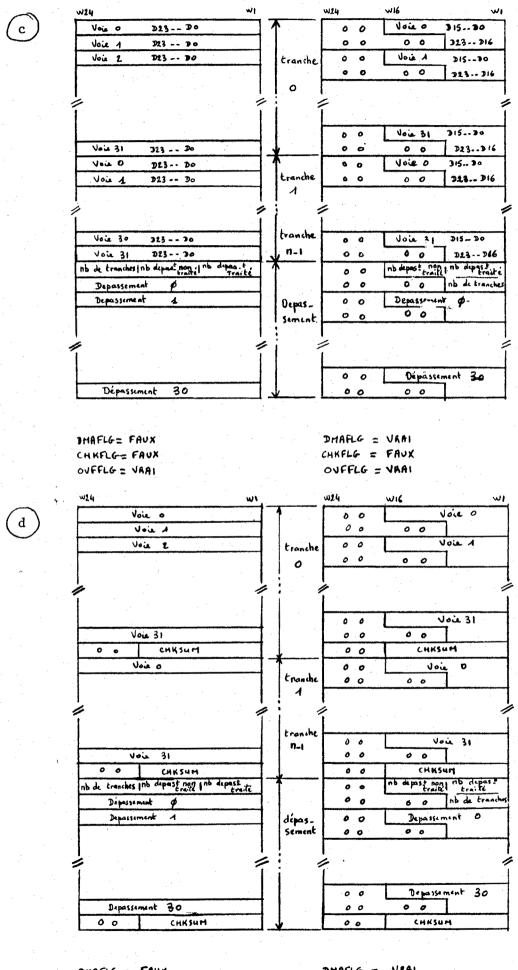

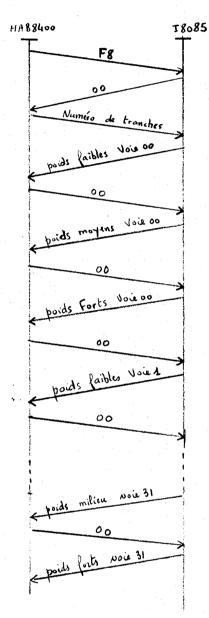

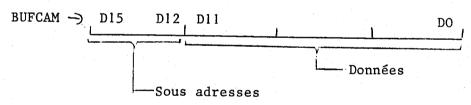

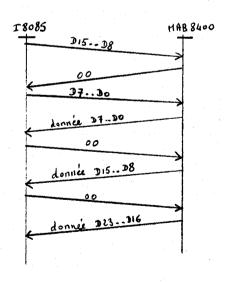

| IV.5.   | Format de sortie des données (compteur 32 voies)               | 105  |

| IV.6.   | Activité du processeur central                                 | 121  |

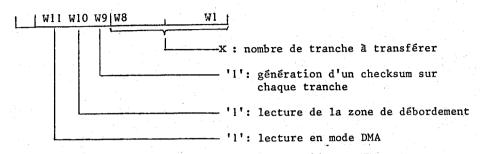

| IV.7.   | Format de sortie des données (synchronisation)                 | 123  |

|         |                                                                |      |

| V.1.    | Organisation de la mémoire image                               | 140  |

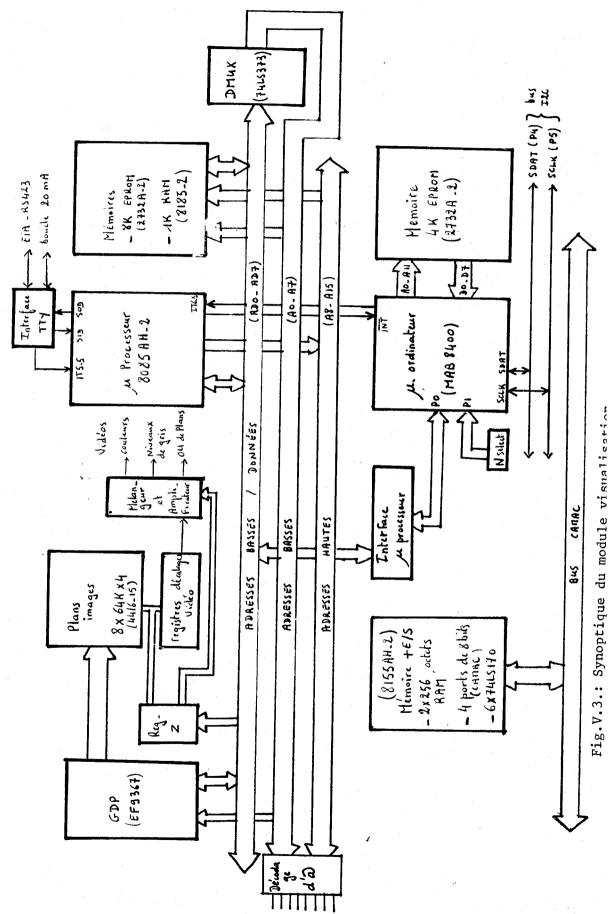

| V.2.    | Période d'activité du GDP                                      | 141  |

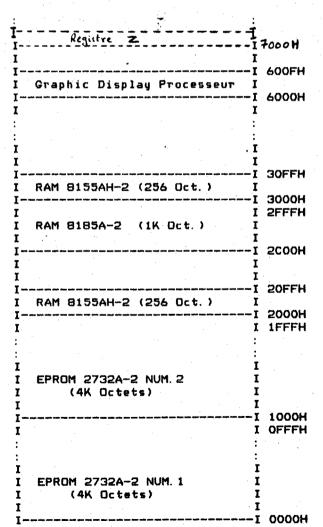

| v.3.    | Synoptique du module visualisation                             | 143  |

| V.4.    | Zones mémoires du module visualisation                         | 142  |

| V.5.    | Sérigraphie de la télétype de poche                            | 162  |

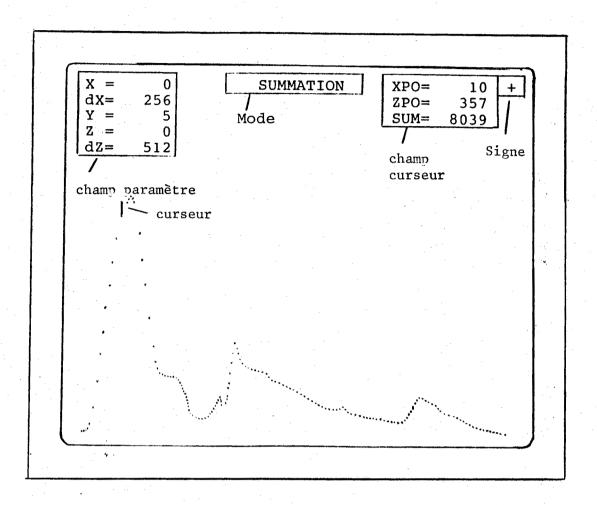

| V.6.    | Organisation de l'image                                        | 163  |

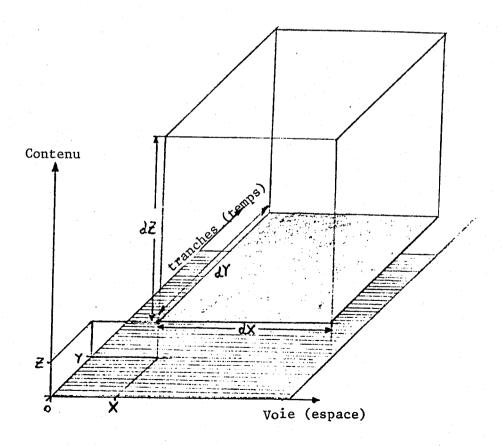

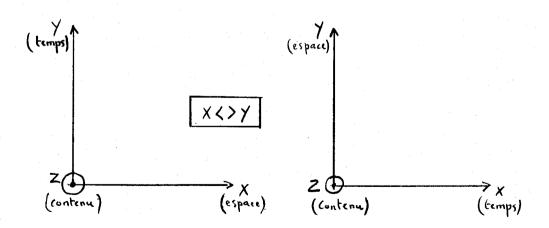

| V.7.    | Représentation des paramètres en 3 dimensions                  | 164  |

| v.8.    | Mode SPECTrum                                                  | 165  |

| V.9.    | Inversion (X()Y) en mode SPECTrum                              | 166  |

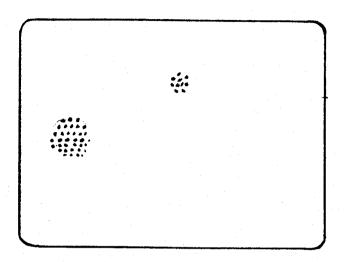

| v.10.   | Visualisation en mode ISOmétrique                              | 167  |

| 77 11   | Visualisation en mode CONTur                                   | 168  |

|       |              |                                                 | Page |

|-------|--------------|-------------------------------------------------|------|

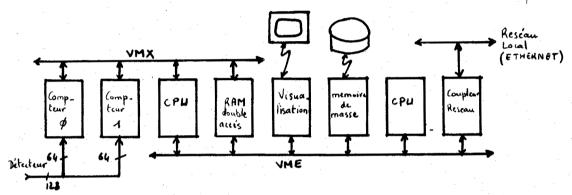

| VI.1. | Architecture | possible pour l'amélioration de t <sub>m</sub>  | 171  |

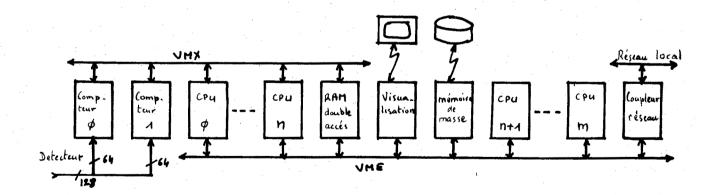

| VI.2. | Architecture | simple pour l'amélioration de t <sub>lmin</sub> | 173  |

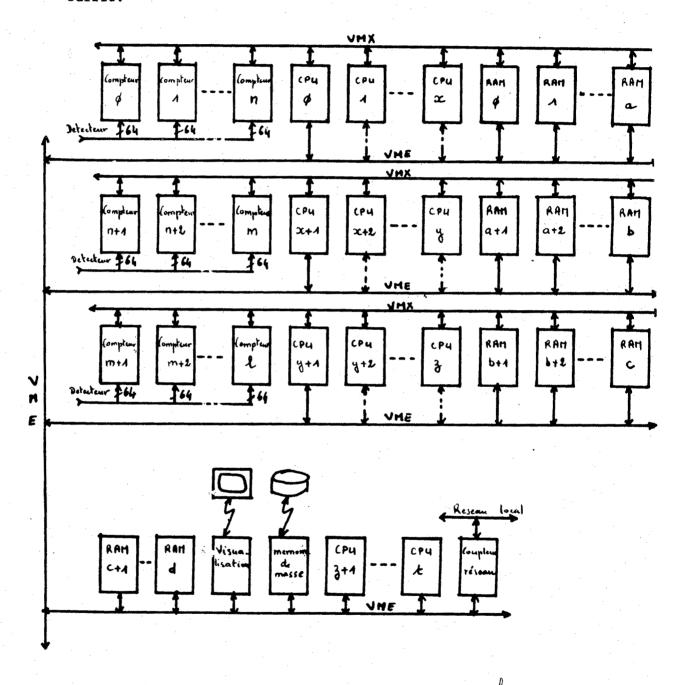

| VI.3. | Architecture | à plusieurs maîtres                             | 173  |

| VI.4. | Architecture | à plusieures branches                           | 174  |

#### SOMMAIRE

Le présent mémoire a pour objet la réalisation matérielle et logicielle d'un système d'acquisition de comptage de neutrons (ou d'évènements).

Un faisceau de neutron envoyé sur un échantillon à étudier est diffracté dans différentes directions. L'étude de ces directions et des longueurs d'ondes donnent des informations sur la constitution interne de l'échantillon.

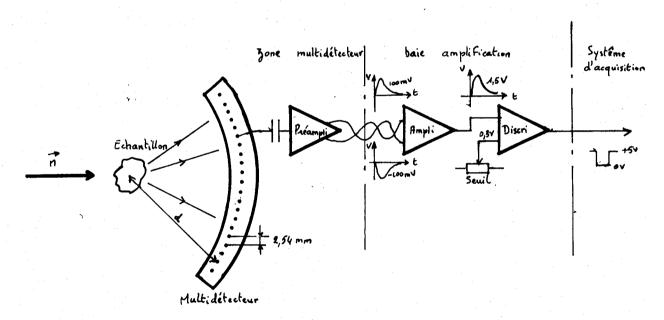

Les neutrons diffractés, localisés par un détecteur ou multidétecteur sont remis en forme par une électronique analogique d'amplification. Les signaux supérieurs à un seuil générent une impulsion logique d'une durée avoisinant la  $\mu s$  (illimination du bruit de fond par discrimination).

Ces impulsions doivent être comptabilisées pendant la durée d'une acquisition. Pour avoir des informations sur l'évolution de processus physique, il est nécessaire d'incrémenter dans différentes zones correspondant aux différents temps (méthode multistroboscopique ou "multiscaling").

L'acquisition terminée les données sont transférées au calculateur de contrôle de processus (transmission parallèle) pour stockage temporaire et prétraitement, puis transmission au calculateur central (réseau local DECNET).

La construction de l'expérience D20 a été le point de départ de cette étude. Cette dernière a donc été menée en étroite collaboration avec les physiciens responsables de cette expérience, tout en ne perdant pas de vue que ce système doit pouvoir être installé sur d'autres expériences (D2, D4, etc...).

Le système d'acquisition a donc été réalisé de façon modulaire et comporte 3 types de modules:

- Compteur 32 voies: module gérant 32 voies d'acquisition.

- Synchronisation: module générant toutes les synchronisations destinées aux modules 'compteur 32 voies'.

- Visualisation: module servant à visualiser le contenu des compteurs pendant l'acquisition.

Les modules sont reliés entre eux par un bus série I2C, constituant un réseau.

#### INTRODUCTION

L'Institut Laue-Langevin (ILL), fondée en 1967 par les gouvernements français et allemand, met à la disposition de la communauté scientifique un flux calibré de neutron ainsi qu'un parc d'expériences.

En janvier 73 la Grande-Bretagne est devenue le troisième partenaire.

Le parc d'expériences couvrent de nombreux domaines qui s'étendent de la physique fondamentale à la biologie en passant par la chimie.

Les propositions d'expériences sont examinées par un conseil scientifique et seulement 70% d'entre elles sont retenues en raison des temps de faisceau limités. Seulement 2000 jours de faisceau par mois sont retenus alors que les demandes sont de 5000.

Les chercheurs invités viennent à Grenoble pour la durée de leurs recherches, et toute l'infrastructure de l'ILL est mise à leur disposition: département, technique, informatique, cryogénique, administratif, etc...

Un programme scientifique est également élaboré à l'ILL et les différents domaines sont répartis en collèges:

- Théorie

- Physique fondamentale et physique nucléaire

- Structures magnétiques et crystallines

- Liquides, défaut dans les métaux

- Biochimie

- Physique chimie / polymères

La direction de l'ILL est assurée par trois directeurs choisis dans chacun des pays membre.

Le personnel comprend actuellement 500 personnes réparties en différents départements (réacteur, technique, scientifique, administratif, etc...).

Les travaux auxquels ce mémoire se rapporte ont été effectués dans le Département Instruments et Méthodes, Service Electronique, chargés du développement de nouveau projet, de l'amélioration d'expériences déjà existantes et de la maintenance.

Le chapitre I sera consacré à l'explication des phénomènes de diffraction neutronique ainsi qu'à l'étude succinte des différents instruments existants à l'ILL.

La première partie du chapitre II traitera du bus CAMAC qui est le standard en physique nucléaire. Une deuxième partie sera consacrée à un bus série type I2C permettant de réaliser un mini réseau de module en standard CAMAC. Ce bus améliorant les performances du CAMAC pour notre application.

Les chapitres III et IV expliquent la philosophie générale du système d'acquisition et traiteront plus particulièrement les deux types de modules réalisés: compteur 32 voies, synchronisation. Le chapitre III sera réservé au matériel alors que le chapitre IV traitera du logiciel.

Le troisième type de module (visualisation des compteurs) sera traité dans le chapitre V.

Le chapitre VI donnera les résultats et parlera des améliorations qui pourraient être apportées au système.

#### I. NEUTRON, NEUTRONIQUE, CAS PARTICULIER DE L'INSTRUMENT D20

#### SYSTEMES D'ACQUISITION DES COMPTAGES DE NEUTRONS

Les appareils de diffusion neutronique utilisent des neutrons produits par un réacteur à fission d'uranium 235, le coeur de ce réacteur étant entouré d'un modérateur à eau lourde à température ambiante: les neutrons rapides produits par la fission (quelques MeV en énergie) sont thermalisés par le modérateur et présentent un spectre en énergie relativement étroit au voisinage de 25 meV. Des tubes tangentiels pénétrant dans le modérateur extraient des faisceaux de neutrons hors de l'enceinte de protection du coeur du réacteur. Ces faisceaux sont utilisés par divers appareils de mesure.

#### I.1. Les neutrons thermiques

#### I.l.l. Caractéristiques

Les neutrons thermiques sortant du modérateur à eau lourde à température ambiante T ont une masse m, une énergie cinétique E de l'ordre de kT, où k est la constante de Boltzmann, une vitesse v et une longueur d'onde associée  $\lambda$  [BAC75] . E, v et  $\lambda$  sont directement reliés par les formules ci-dessous:

masse:  $m = 1,675.10^{-24}g$

énergie:  $E = \frac{1}{2} \text{ mv}^2 = kT$  avec  $k = 1,38 \times 10^{-23}$  JK-1

vitesse: v

longueur d'onde:  $\lambda = \frac{h}{mv}$  avec  $h = 6,62 \times 10^{-34}$  J.A (constante de Planck)

Le neutron possède un spin ou moment magnétique.

Le spectre en énergie relativement étroit d'environ 5 meV à 100 meV est représenté sur la figureI.1, courbe l

Figure II: Spectres du flux de neutrons thermiques

Le flux au nez du canal de sortie par unité de longueur d'onde  $\lambda$  (en A) et unité d'angle solide (en stéradian) est tracé en fonction de la longueur d'onde  $\lambda$  (en Å).

À est l'unité la plus couramment employée par les "diffractionistes" et correspond à 10-10 m ou 0,1 nm.

Pour disposer de neutrons d'énergie ou de longueur d'onde différentes de ceux produits par le modérateur à température ambiante, deux sources de petites dimensions ont été placées dans le modérateur: une source chaude constituée d'un bloc de graphite à 2000 K et une source froide (deuterium liquide à 20 K). Les spectres des flux de neutrons produits par ces sources sont représentés sur les courbes 2 (source chaude) et 3 (source froide) de la figureII.

#### I.l.2. Interaction neutron-matière

Le neutron thermique peut avoir deux types d'interaction avec la matière: capture ou diffusion.

Le phénomène de capture du neutron, par exemple dans des réactions nucléaires avec un atome d'uranium 235, de bore 10, d'hélium 3, etc. est gênant lorsqu'il se produit dans un échantillon dont on veut étudier la structure interne. Ce phénomène de capture est par contre utilisé pour détecter les neutrons ou pour arrêter les neutrons inutiles (protections diverses).

La diffusion des neutrons, qui ont une masse et un spin ou moment magnétique, est gouvernée par les chocs neutrons-noyaux et neutrons-moments magnétiques dans la matière. La longueur d'onde des neutrons thermiques, quelques Å, est une distance interatomique typique. Les neutrons thermiques subissent des réflexions de Bragg sélectives [BAC 75] données par la formule.

#### 2d $\sin \theta = \lambda$

où d est la distance entre deux plans d'atomes dans un cristal (atomes empilés régulièrement),  $\lambda$  la longueur d'onde des neutrons et  $\theta$  l'angle d'incidence des neutrons par rapport au plan d'atomes (Fig. 2).

Figure T2: Réflexion de Bragg sur une famille (1) de plan atomique d'un cristal. Le cristal possède beaucoup d'autres familles de plan atomique: (2) etc.

On dit qu'il y a diffraction élastique si les neutrons diffusés garder leur énergie ou longueur d'onde initiale. Si les neutrons diffusés ont perdu ou gagné de l'énergie dans le processus d'interaction avec la matière, on a affaire à la diffusion inélastique, la variation d'énergie de neutron donnant alors une information sur les mouvements internes des atomes du matériau.

#### I.2. Les grandes familles d'appareils de diffusion neutronique

Il y en a deux. Les appareils utilisant la diffraction élastique, avec la loi de Bragg, permettent d'étudier la structure microscopique de la matière, de déterminer les positions des atomes les uns par rapport aux autres. Ce sont les diffractomètres, appareils dénomés D suivi d'un numéro d'ordre à l'ILL; exemple D3, D15, D20. Les appareils qui permettent d'analyser les mouvements internes des atomes d'un matériau grâce à la diffusion inélastique des neutrons sont appelés IN suivi d'un numéro d'ordre à l'ILL; exemple: IN3, IN5,...

Quelques autres appareils existant à l'ILL fonctionnant sur d'autres principes, utilisent des techniques spéciales.

Une description précise et complète des différents types d'appareils de diffusion neutronique est faite dans le livre de GE BACON [BAC 75], et la description détaillée des caractéristiques des instruments existant ou en construction à l'ILL se trouve dans le livre cité en référence [NRF83].

#### I.2.1. Les diffractomètres

#### I.2.1.1. Diffractomètres 4 cercles pour monocristaux

Ces instruments ont 3 éléments (figI.3). Un monochromateur M placé dans le faisceau réacteur, est orienté avec un angle  $\Theta_M$  pour réfléchir dans la direction 2  $\Theta_M$  une partie du spectre réacteur représenté, en figure I.l.Seuls les neutrons satisfaisants à la loi de Bragg ( 2d sin  $\Theta_M$  =  $\lambda$ ) seront réfléchis vers l'échantillon E.

On choisit d distance interatomique et 2  $\theta_{\rm M}$  pour sélectionner la longueur d'onde  $\lambda$  désirée, avec typiquement  $\frac{\Delta\lambda}{\lambda} \leq 1\%$ .

L'échantillon (un cristal) est installé sur un ensemble mécanique G comportant 3 mouvements de rotation pour permettre une orientation de E dans toutes les directions de l'espace, et mettre successivement en position de reflé-xion chacune des familles de plan atomique du cristal.

Un détecteur de neutron D tourne autour de l'échantillon (angle  $2\theta_E$ ) pour aller compter les neutrons diffractés par le cristal. Cet angle  $2\theta_E$  est le 4ème cercle.

FigI.3:Principe d'un diffractomètre à 4 cercles.

## I.2.1.2. Diffractomètres à 2 axes (étude des poudres, liquides)

Le schéma est identique à celui de la figureI3, avec l'ensemble échantillon et mouvements d'orientation G remplacés par une poudre qui est une multitude de plans atomiques. Il y a un certain nombre de cristaux en position de réflexion, donnant un pic de Bragg avec l'angle  $2\theta_E$  par rapport au faisceau monochromatique. On a ainsi un cône de diffraction ayant pour axe le faisceau monochromatique et pour demi angle au sommet  $2\theta_E$  (voir fig.I.4).Il en est de même pour les autres familles de plans atomiques, avec d'autres valeurs de  $2\theta_E$  caractéristiques des distances interatomique.

On déplace le détecteur D en pas-à-pas dans le plan horizontal, ou on utilise un détecteur de localisation ou multidétecteur qui "photographie" simultanément tous les points du diagramme.

Fig.I.4.: Diffractomètre à 2 axes avec les cônes de diffractions.

En haut: méthodes classiques

du détecteur en

pas-à-pas.

En bas: multidétecteur

Fig.I.5. Diagramme de 2 poudres typiques

La Figure I.5 montre deux diagrammes de poudre: le silicium a une structure cubique très simple (peu de pics). L'alumine a une structure plus complexe (diagramme plus fourni).

#### I.2.2. Les appareils de diffusion inélastique

On s'intéresse aux neutrons diffusés par un échantillon recevant un faisceau monochromatique comme pour les diffractomètres, mais on veut en plus connaître la variation d'énergie (ou de longueur d'onde) de ces neutrons diffusés. Deux méthodes existent:

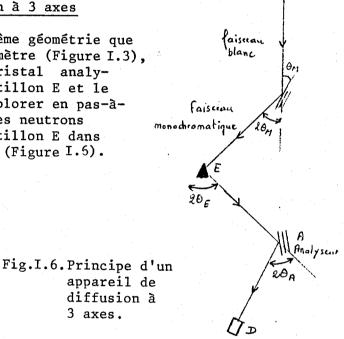

#### I.2.2.1. Appareil de diffusion à 3 axes

On a exactement la même géométrie que celle d'un diffractomètre (Figure I.3), mais on utilise un cristal analyseur A entre l'échantillon E et le détecteur D, pour explorer en pas-àpas la répartition des neutrons diffusés par l'échantillon E dans une direction donnée (Figure I.6).

Reacteur

# I.2.2.2. Appareils de diffusion inélastique à temps de vol

Figure I.7. Principe d'un appareil de diffusion inélastique à temps de vol.

3 axes.

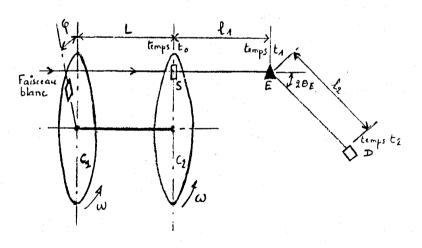

Un ensemble de 2 "choppers" (Figure I.7) constitués chacun d'un disque absorbant les neutrons sauf sur une petite ouverture est placé dans l'axe du faisceau blanc. Ces deux disques sont couplés mécaniquement sur le même axe tournant à une vitesse élevée  $\omega$ .

Les ouvertures des disques choppers Cl et C2 sont décalés d'un angle  $\varphi$ . Seuls les neutrons étant passés par la fente de Cl et ayant une vitesse bien déterminée (relation directe entre 1,  $\omega$  et  $\varphi$ ) passeront la fente de C2 au point S. On a en S une source de pulses de neutrons monochromatiques.

Ces neutrons passés en S au temps  $t_0$  parcourent la distance  $l_1$  en un temps déterminé  $t_1$  et calculable d'après l,  $\omega$ ,  $\varphi$  et  $l_1$ . Après diffusion par l'échantillon E, ils sont localisés dans le détecteur au temps  $t_2$ . Le temps  $(t_2 - t_1)$  mis pour parcourir, la distance  $l_2$  permet de calculer l'énergie des neutrons après diffusion par E.

#### I.3. Cas particulier de l'instrument D20

Des diffractomètres équipés de multidétecteurs (exemple DIB NRF 83) existent à l'ILL et permettent depuis longtemps d'obtenir des diagrammes de diffraction de poudre en un temps court (2 à 10 mn). Cette rapidité d'obtention des diagrammes sur un grand domaine angulaire est mise à profit pour suivre une évolution lente d'un échantillon en fonction par exemple de la température du cristal. Un autre exemple serait celui d'une réaction chimique lente (2 à 10 heures) et irréversible telle que:

$$A + B \rightarrow C$$

(cas simple)

Les matériaux A, B et C ont chacun des structures connues, donnant des pics de Bragg bien localisés en 20. L'intensité des pics est répresentative des masses A, B et C a un instant donné. En effectuant de nombreux diagrammes au cours de la réaction chimique, on a accès à la vitesse de réaction. Dans certains cas il est possible, d'observer des produits intermédiaires existants en cours de réaction [RIE 80], [RIE 83].

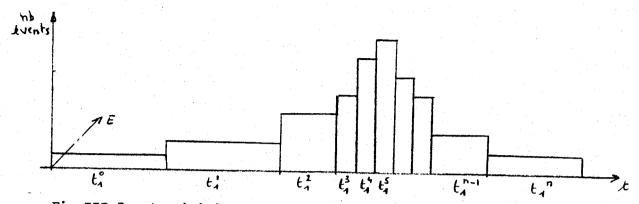

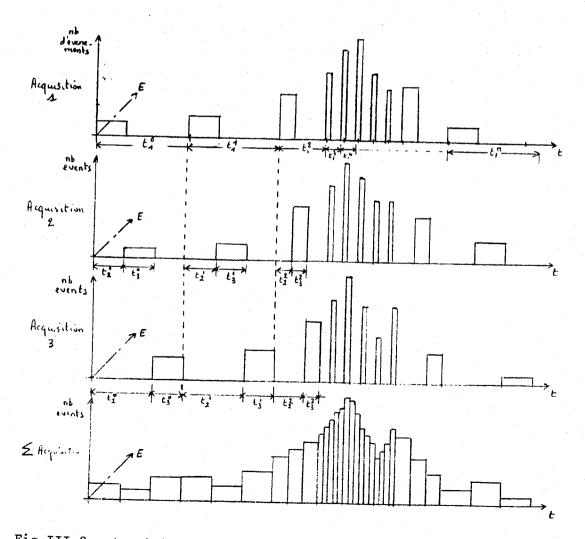

Si on s'intéresse à des phénomènes cinétiques plus rapides, les taux de comptage pour un diagramme sont trop faibles. Si le phénomène est reproductible, on peut atteindre des comptages suffisants en cyclant de nombreuses fois l'expérience (méthode stroboscopique). C'est le cas pour certaines réactions électrochimiques, ou la vibration mécanique d'un resson Si on veut étudier le phénomène cinétique complet on divise le cycle en plusieurs tranches de temps, donnant alors autant de diagramme de diffraction (voir III.4.2.). On peut alors parler de methode "multistroboscopique ou "multiscaling".

Les spécifications concernant le système d'acquisition des comptages neutroniques du diffractomètre D20 particulièrement adapté à ce type nouveau d'expérience à l'ILL, sont décrites dans un document cité en référence [ILL 82].

Plus récemment Oberthür  $\begin{bmatrix} 0BE & 84 \end{bmatrix}$  à demontré les limites de la résolution en temps, c'est-à-dire la durée minimale d'une tranche de temps. Cette limite est de l'ordre de 10  $\mu S$  pour D20.

#### I.4. Systèmes d'acquisition des comptages de neutrons

En fonction des familles d'appareils, différents systèmes d'acquisition ont été développés à l'ILL.

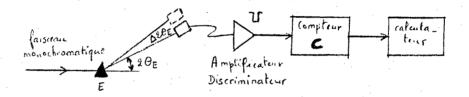

#### I.4.1. Monodétecteur et chaîne d'acquisition

La version la plus simple d'un appareil est celle ayant un unique détecteur (monodétecteur)D, que l'on déplace en pas-à-pas autour de l'échantillon E (figure I.8.). A ce détecteur est associé une chaîne d'acquisition de comptage de neutron C. A chaque fin de temps d'acquisition on vient lire et remettre à zéro le compteur par le calculateur, puis on déplace le détecteur d'un angle  $\Delta 2\theta_E$  très faible (quelques centièmes de degrés) et on redémarre un nouveau comptage. Le diagramme de diffraction est ensuite reconstitué.

Figure I.8.: Principe d'un appareil avec monodétecteur et chaîne d'acquisition unique.

Cette architecture est très employée pour les appareils de diffusion inélastique. Pour les diffractomètres, elle présente l'avantage d'avoir un détecteur et une chaîne d'acquisition très simple donc fiable. Par compte les temps de mesure sont très longs en raison de la nécessité de réconstituer le diagramme de diffraction.

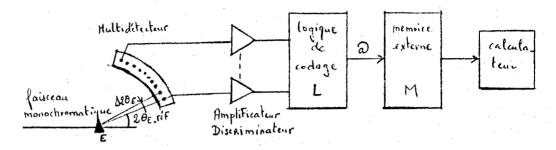

#### I.4.2. Multidétecteur et mémoire externe

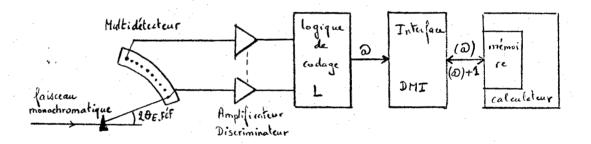

Pour éviter de déplacer le détecteur autour de l'échantillon on a créé les multidétecteurs, qui sont des ensembles de détecteurs unitaires, ou une grille de fils (généralement au pas de 2,54 mm), qui permettent d'avoir une vision instantannée du diagramme de diffraction Pour chaque détecteur ou chaque fils on a des préamplificateurs, amplificateurs et discriminateurs. Un neutron diffracté est détecté sur plusieurs fils adjacents. Un calcul de barycentre est effectué par la logique de codage L afin de localiser l'endroit exact de l'évènement. Les différents évènements sont stockés dans une mémoire M, externe au calculateur qui effectue l'opération:  $(\hat{O})$ : =  $(\hat{O}+1)$  pour comptabiliser les neutrons.  $\hat{O}$  étant l'adresse de la réaction.

Figure I.9.: Principe d'un appareil avec multidétecteur et mémoire externe.

L'électronique d'acquisition est beaucoup plus volumineuse car elle nécessite une chaîne d'amplification par détecteur ou par fils. Par contre les temps de mesure sont beaucoup plus courts.

### I.4.3. Multidétecteur + Incrémentation Directe en mémoire calculateur (DMI)

Une autre solution consiste à incrémenter directement en mémoire centrale du calculateur (figure I.10.).

Figure I.10.: Principe d'une acquisition de comptage en incrémentation directe en mémoire centrale du calculateur.

Avec cette architecture on économise le dispositif de mémoire externe, mais lorsque le taux de comptage est important, le calculateur est toujours en cycle DMI et les autres tâches ne peuvent être effectuées.

#### I.4.4. Multidétecteur + chaîne individuelle de comptage

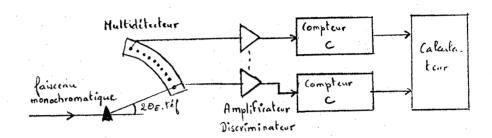

Le système décrit en I.4.2. associant une logique de codage L et une mémoire externe M limite le taux de comptage sur l'ensemble du détecteur à 500 K évènements/seconde. En associant une chaîne de comptage par détecteur ou par fils on arrive à des taux de comptage de l M énènements/seconde par voie (Figure I.11.).

Figure I.ll.: Principe d'une acquisition avec une chaîne de comptage par détecteur ou fils.

#### I.4.5. Introduction des mesures cinétiques

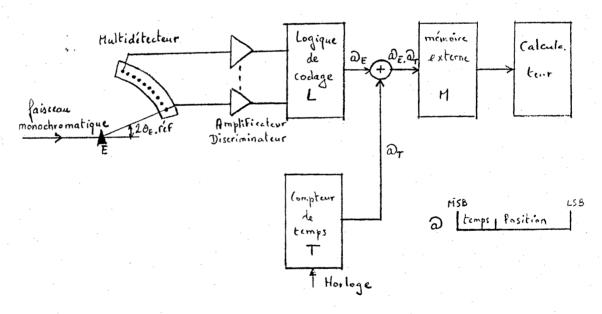

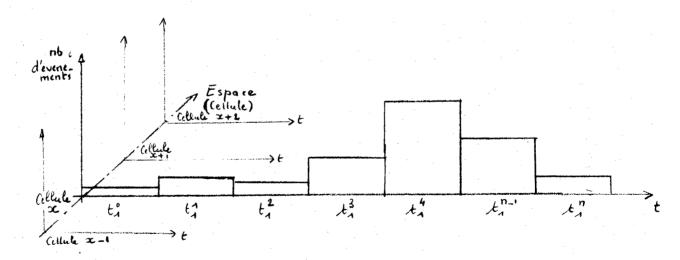

Des expériences classiques du type décrit en I.4.2. ont été étendues pour réaliser des mesures cinétiques. Ces extensions consistent à ajouter une information de temps à l'information d'emplacement ou d'espace (Figure I.12.).

Fig.I.12.: Principe d'une acquisition de comptage en cinétique.

En fin d'expérience le contenu de la mémoire externe représente différents diagrammes de diffraction à des temps différents.

| diagramme | l diag | amme 2 |  | <br>diagramme n |

|-----------|--------|--------|--|-----------------|

| ,         |        |        |  |                 |

| temps 1   | ten    | nps 2  |  | temps n         |

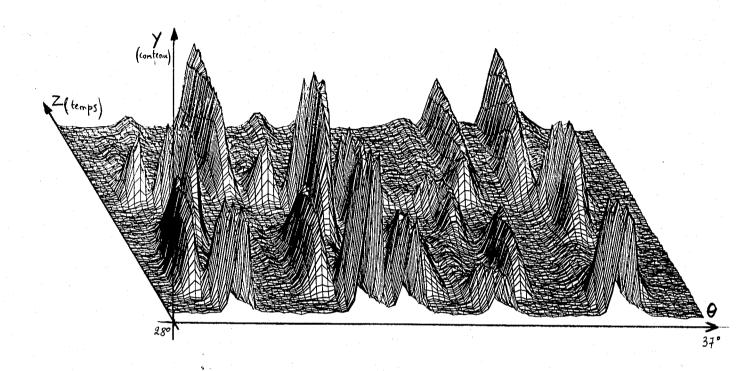

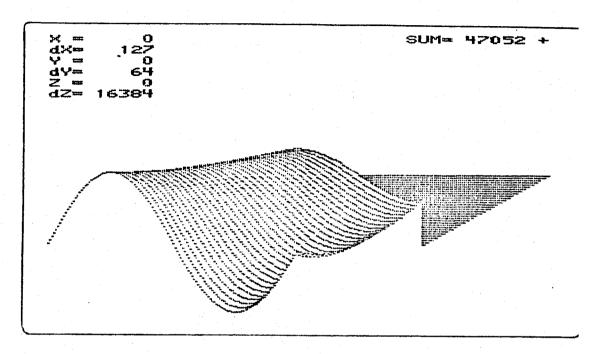

Ces diagrammes peuvent être interprétés graphiquement (Figure I.13.)

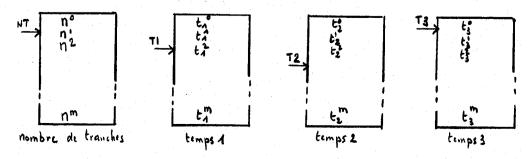

Fig. I.13.: Interprétation graphique de mesure cinétique (DIB 6 Mars 1984)

Le temps est lié à une température.

#### II. DESCRIPTION DES BUS UTILISES

### II.1. Description CAMAC [EUR 72]

La communauté scientifique Européenne de l'Energie Atomique (EURATOM) a adopté en 1969 le standard CAMAC (Computer Automated Measurement And Contro L'Institut Laue-Langevin dès sa création en 1971 a également opté pour ce standard.

Le standard définit à la fois les normes électroniques et mécaniques.

Le CAMAC est un système modulaire composé de modules enfichés dans un chassis. Chaque module utilise une ou plusieurs unités dans le chassis.

Les chassis sont montés dans une baie 19 pouces et ont 25 stations pour enficher des modules. Les modules ont une hauteur minimum de 5 unités (1 Unité = 44.45 mm).

Dans un même chassis, les modules sont connectés entre eux par un bus en face arrière (DATAWAY) de 86 signaux ayant différentes fonctions:

- 24 lignes "Write": lignes d'écriture de données dans le module,

- 24 lignes "Read": lignes de lecture de données dans le module,

- 5 lignes "Function": lignes de fonction qui définissent le type d'opération que le module doit effectuer,

- 4 lignes "Sub Adresse": lignes de sous adresses permettant d'accéder à des sous ensembles d'un module,

- lignes d'initialisation: Z, C, Inhibit,

- Timing: S1, S2: strobe 1 et 2,

- Alimentations:  $\pm 6v$ ,  $\pm 12v$ ,  $\pm 24v$ ; 200v, 127VAC,

- 5 lignes non standard: Disponibles pour l'utilisateur. (Pl..P5)

De plus, chaque module est connecté par deux lignes individuelles L(Look at me) qui est une demande d'interruption et N (Numéro module) permettant d'adresser les modules (Fig. II.1.)

En position 25 se trouve le contrôleur de chassis qui est le maître des 24 autres modules esclaves et qui permet le dialogue avec le calculateur.

Un ordre du maître vers un esclave est composé des signaux N pour la sélection du module et des signaux bus, A (Sous-adresses), F (Fonctions), et éventuellement données lues (R) ou écrites (W), ainsi que des signaux de timing S1 et S2 (Voir figure II.2.)

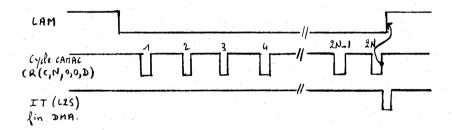

Lorsqu'un esclave désire être servi il a la possibilité de positionner son signal LAM (Look At Me). Ce signal génère une interruption au module contrôleur. Selon l'intelligence de ce contrôleur, l'interruption peut être servie par celui-ci ou envoyée au calculateur.

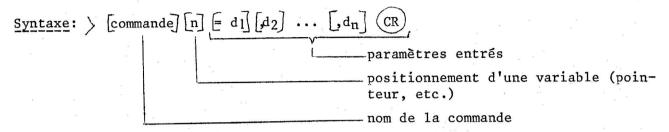

Le calculateur peut adresser plusieurs chassis, donc dans la suite de ce mémoire, les fonctions CAMAC seront écrites de la façon suivante:

CW (C, N, A, F, D); CR (C, N, A, F, D); CF (C, N, A, F)

C = numéro de chassis

N = numéro de module

A = sous-adresses

F = fonctions

D = donnée

CW, CR, CF: fonctions CAMAC

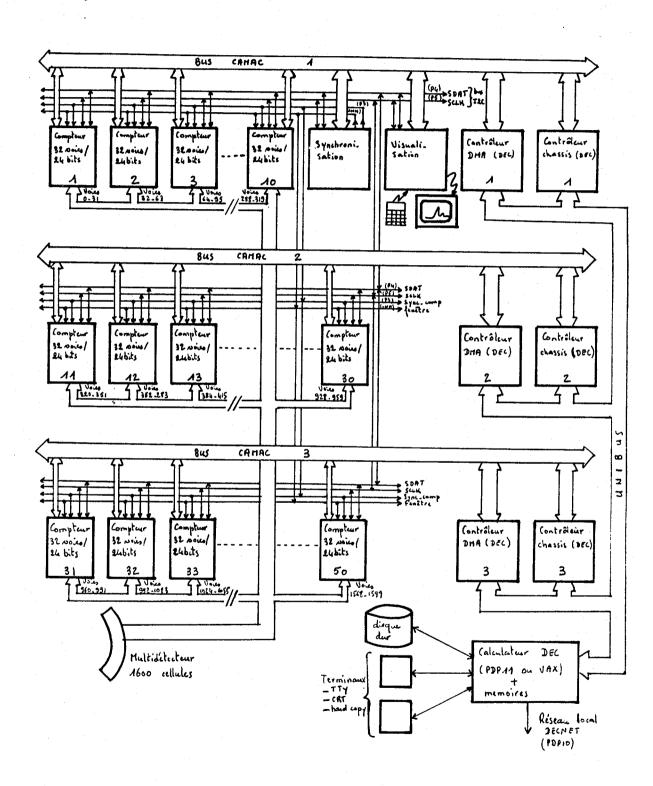

Fig. II.2.: Diagramme des temps d'une fonction CAMAC

Le projet original D20 comportait 1600 voies de comptage. Après étude du taux d'occupation, fonction des circuits intégrés nécéssaires, nous avons décidés de réaliser des modules gérant 32 voies chacun. Ceci impliquait d'avoir 50 modules. Par le fait que le standard CAMAC gère les modules un par un, il aurait fallu effectuer chaque commande 50 fois. Nous avons donc décidé de connecter tous ces modules sur un bus série type I2C (Inter Integrated Circuit) décrit dans le paragraphe suivant.

Ce bus série occupe les lignes à la disposition de l'utilisateur (P4 et P5) et a pour but de réaliser un mini-réseau local fonctionnant selon la méthode CMSA/CD (Carrier Sense Multiple Access with Collision Detection).

## II.2. Bus I2C [RTC 81]

Le bus I2C est un bus bidirectionnel permettant de transmettre des données en série en utilisant deux lignes: horloge, donnée.

Il permet la connexion aisée entre plusieurs micro-ordinateurs, afin de former un réseau, pouvant être multi maître, multi esclave, pour un coût relativement bas.

Ce bus a été mis au point par les fabricants de circuits intégrés Philipps et RTC. Ces circuits sont en fait des micro-ordinateurs de type I8048 (Intel auxquels on a rajouté la fonction de gestion du bus I2C.

La famille de circuits intégrés comprend également des mémoires RAM, ROM, des compteurs temporisateurs, des afficheurs. Ces circuits étant tous accessibles par le bus série.

Pour notre application nous n'utilisons que le circuit micro-ordinateur référencé MAB 8400.

La gestion du bus étant entièrement implementée par ce micro-ordinateur ceci évite d'avoir à scruter le bus et d'effectuer un filtrage numérique par logiciel des informations transitant. En effet, l'interface spécialisé n'interrompt le processeur que lorsqu'il est concerné par les informations, transitant sur le bus. L'unité centrale est alors libre pour effectuer d'autres tâches.

#### II.2.1. Fonctionnement

La conception de l'interface d'entrée sortie série permet l'interconnexion d'un grand nombre de circuit de la famille MAB 8400 (jusqu'à 127) ayant chacun une adresse particulière sur 7 bits. Deux processeurs (ou plus) peuvent communiquer entre eux sans la moindre interruption des autres. L'adresse 00 constitue une adresse générale pour tous les processeurs.

Quatre modes de fonctionnement sont possibles:

- Maître émetteur: le processeur maître génère l'horloge et les

données vers les processeurs esclaves.

- Maître récepteur: le processeur maître génère l'horloge; le processeur esclave génère les données.

- Esclave récepteur: le processeur esclave reçoit l'horloge et les données venant du maître.

- Esclave émetteur: l'esclave envoie les données en synchronisme avec l'horloge générée par le maître.

Le sens de transfert est donné par le bit le moins significatif du premier mot émis.

#### Bus de donnée série

Deux lignes bidirectionnelles: SCLK (Horloge)

SDAT (Donnée)

Le bus est régi selon deux règles:

- Le transfert ne peut être initialisé que si le bus est libre.

- Pendant le transfert la ligne de donnée doit rester stable lorsque la ligne horloge est haute. Des changements sur la ligne donnée lorsque l'horloge est haute correspondent à des signaux de contrôle (Fig. II.3.)

- l: bus libre

- 2: Prise de bus: } sur SDAT. Alors que SCLK est haut

- 3: Changement de SDAT. Lorsque SCLK-est bas

- 4: SDAT stable lorsque SCLK est haut

- 5: fin de message: f sur SDAT. Alors que SCLK est haut

Fig. II.3.: Différentes phases d'un échange sur le bus I2C

#### Mécanisme d'interruption

L'interruption de l'interface bus série vers le processeur est générée dans les cas suivants:

- un mot complet a été émis ou reçu.

- l'adresse d'appel général a été reçue (oo)

- l'adresse d'appel individuel a été reçue

La ligne d'horloge est maintenue stable tant que les interruptions à la fois dans le maître et dans les esclaves n'ont pas été servies. Cela permet de garder la maîtrise du bus, mais demande des traitements rapides.

Fig. II.4.: Synchronisation de deux noeuds du réseau

#### Arbitrage de bus et gestion des collisions

Dès qu'un processeur a généré un début de message un indicateur "bus occupé" est positionné dans tous les processeurs, empêchant ces derniers d'initialiser un transfert.

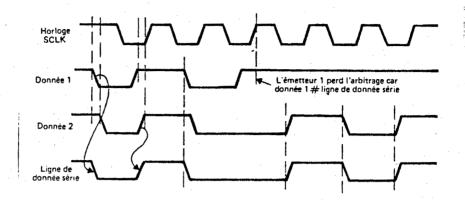

Il est tout de même possible que plusieurs processeurs initialisent un transfert au même instant. Pour arbitrer cette collision chaque processeur vérifie que le bit qu'il vient de positionner n'a pas été forcé. Si un bit a été forcé par un autre processeur demandant le bus, ce processeur perd le bus, positionne un indicateur et génère une interruption à l'unité centrale (voir fig. II.5.)

Fig. II.5.: Arbitrage entre deux maîtres demandant le bus

Par ce fait on voit qu'une priorité matérielle existe. En effet le processeur émettant la donnée binaire la plus petite accédéra au bus, alors que les autres processeurs le perdront.

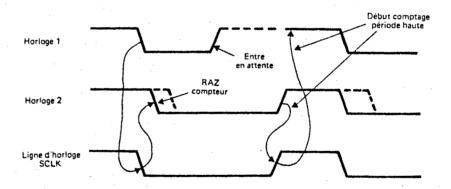

Par le même type de circuit, les vitesses des processeurs se synchronisent. Les échanges se feront au rythme du processeur le plus lent (vois figure II.6.).

Fig. II.6.: Synchronisation des horloges

#### Travail en mode acquittement

Lorsqu'on travaille en mode acquittement, le maître génère une impulsion d'horloge supplémentaire afin que le récepteur positionne la ligne donnée à '0'. Ceci permet de tester si la donnée a bien été reçue (ou envoyée), et également de savoir si le processeur adressé est bien connecté au bus (fig. II.7.)

Fig. II.7.: Travail en mode acquittement

### II.2.2. Application

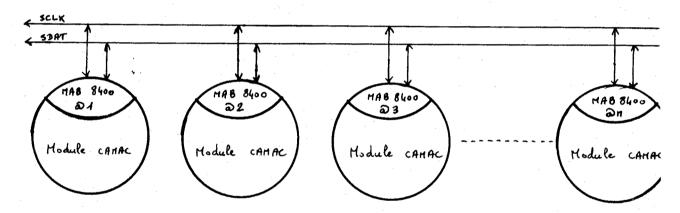

A l'aide des processeurs MAB 8400 nous avons réalisé un mini réseau de type bus linéaire fonctionnant sur le module CSMA/CD (Carrier Sens Multiple Access with Collision Detection) où chaque noeud est un module CAMAC (voir figure II.8.).

Fig.II.8.: Réseau de modules CAMAC

Par rapport à la norme ISO nous trouvons:

- Au niveau physique: Utilisation des lignes P4 et P5 du bus CAMAC réservées à l'utilisateur. Ces lignes sont de types bus réalisées soit par un circuit imprimé, soit par câblage (généralement connexions enroulées).

- Les 6 autres niveaux sont confondus en un seul.

Les messages à transmettre peuvent être classés en deux catégories:

1. Simple: Qui ne demande pas de réponse.

Exemple: Remise à zéro d'un registre Démarrage comptage Arrêt comptage Demande états 2. <u>Dialogue</u>: Nécéssitant un temps de réponse long, et donc une libération du bus et une réponse différée.

Exemple: Lecture codeur d'angle

Lecture d'un spectre pour visualisation

Déplacement motorisé

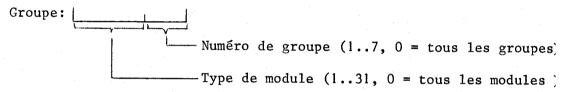

Il est nécessaire de réaliser des groupements de module de même fonction. Par ce fait on a deux trames de messages possibles.

### 1. Individuel

ST+(dest+R/₩)+(Source+o)+(donnéel)+...+(donnée n)+ Stop

### 2. Groupement

ST+(oo)+(groupe)+(Source+o)+(donnée 1)+...+(donnée n)+ Stop

Note: Les données comportent éventuellement en dernier octet un 'checksum' ou un CRC.

En mode adressage de groupe, l'adresse d'appel générale (oo) est envoyée et interrompt tous les processeurs connectés au bus I2C. A l'arrivée du deuxième octet, les processeurs non concernés par la suite du message se déconnectent. Ce type d'adressage permet une grande souplesse d'utilisation, un module pouvant appartenir à plusieurs groupes.

### Aspect pratique:

L'adresse individuelle est matérielle et donnée par 7 clés implantées sur le module.

Les adresses de groupe sont spécifiées par logiciels.

### Exemple:

| Type de module       |   | $\widehat{\mathcal{J}}$ individuelle | a groupe |         |

|----------------------|---|--------------------------------------|----------|---------|

|                      |   |                                      | type     | groupes |

| Compteurs 32 voies l |   | 1                                    | 1        | 1.2     |

| 11                   | 2 | 2                                    | 1        | 1,2     |

|                      | : | :                                    | :        | 1,7     |

| "                    | n | 50                                   | 1        | 1,7     |

| Synchronisation      |   | 51                                   | 2        | 1       |

| Visualisation        |   | 52                                   | 3        | 1       |

| Commande moteur 1    |   | 60                                   | 4        | 1.5     |

| " 2                  | ? | 61                                   | 4        | 1,7     |

| :                    |   | •                                    | •        | 1.2     |

| u n                  | ì | 69                                   | 4        | 1.      |

| Autres modules       |   | 90                                   | 12       | 7,3,4   |

### Performance

La vitesse de transmission est fonction de la vitesse de l'horloge du micro ordinateur; éventuellement divisée par un facteur interne. La fréquence maximale de l'horloge étant de 4.43 MHz et le facteur de division minimum étant de 10 on a:

$$F_{H_{max}} = \frac{F_Q}{3F_C} = \frac{4,43 \cdot 10^6}{3 \times 10} \# 14 \text{ 8 kHz ou } 148 \text{ kbauds.}$$

Cette fréquence correspond à la vitesse de transmission d'un bit, mais on a vu plus haut que l'on envoie au maximum un octet et qu'entre chaque octet le bus reste occupé afin que les ordinateurs effectuent certains traitements.

Si l'on appelle T le temps de transmission d'un octet, W le temps mort entre deux transmissions et N le nombre d'octets à transmettre, on peut calculer le taux de transfert utile:

Taux de transfert utile avec la trame de type l (adresse individuelle):

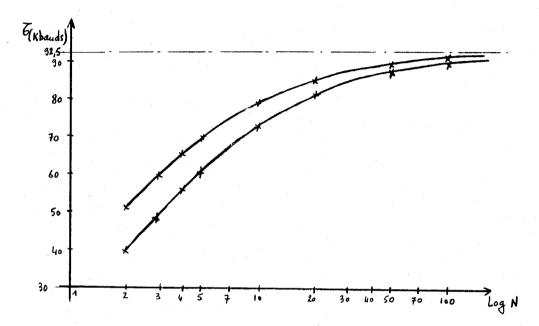

$$\overline{\zeta_1} = \left(\frac{NT}{2T+W+(W+T)N}\right)$$

FH

Fréquence horloge

Transmission d'un octet + temps mort

Transmission de l'entête du message

Taux de transfert utile avec la trame de type 2 (adressage d'un groupe):

$$\epsilon_2 = \left(\frac{NT}{3T+2W+(W+T)N}\right) F_H$$

Si 7<sub>1</sub> ou 7<sub>2</sub>→∞on a:

$$\mathcal{E} = \left(\frac{NT}{(W+T)N}\right) F_{H} = \frac{TF_{H}}{W+T} = \frac{F_{H}}{W/T+1}$$

Exemple: Si W = 0,6T ⇒ W/T = 0,6 cas de l'algorithme donné au chapitre suivant

$$\overline{c}_{1} = \frac{\text{NTF}_{H}}{2\text{T}+0,6\text{T}+1,6\text{TN}} = \frac{\text{NF}_{H}}{2,6+1,6\text{N}}$$

$$Z = \frac{NT \ F_H}{3T+1,2T+1,6TN} = \frac{NF_H}{4,2+1,6N}$$

Si

$$\mathbb{Z}_1$$

ou  $\mathbb{Z}_2 \rightarrow \infty$  on a:  $= \frac{F_H}{W/T+1} = \frac{148 \text{ kbds}}{1,6} = 92,5 \text{ kbauds}$

Les plus courts messages transmis comportent le plus fréquemment 2 octets, on a donc:

- $-Z_1 = 51$  kbauds

- -72 = 40 kbauds

Fig. II.9.: Taux de transfert en fonction du nombre d'octets transmis

En conclusion nous dirons qu'il est très important de minimiser au maximum le temps d'attente entre la transmission (ou la réception) de deux octets. Il est donc nécessaire d'étudier le programme et de faire le maximum de calcul pendant la transmission (ou la réception) de l'octet.

# II.2.3. Algorithme de gestion du bus I2C

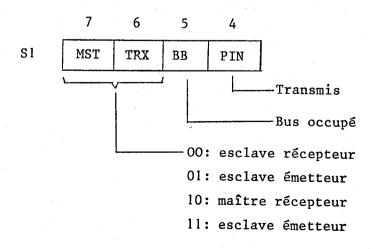

Ci-dessous sont donnés les algorithmes de gestion du bus I2C. Les drapeaux: bus occupé, transmis, arbitration perdue, maître émetteur, esclave récepteur sont les différents bits du registre SI du micro-ordinateur MAB8400 (SI = état du bus I2C). SO est le registre qui réalise la converstion parallèle série. Toutes les autres variables sont globales pour toutes les procédures.

PROGRAMME: PROCES;

FIN;

```

CONST

numpooli

VAR

adr_recept; cpt: ENTIER;

P: POINTEUR;

bufi,bufo: VECTEUR;

DEBUT

A: F:=bufo

cpt:={longueur du buffer}

ASKBUS;

SI P<> 0 ALORS ALLER_A { perte de l'arbitrase }

B:

F:=80H

TANT_QUE P<> O FAIRE RIEN

TRAITER;

ALLER_A B

FIN;

PROCEDURE: ASKBUS;

DEBUT

TANT_QUE bus_occupe FAIRE RIEN

SO:=bufo[P];

TANT_QUE NON transmis FAIRE RIEN {Attente fin transmission:

SI arbitr_perdue ALORS ESCLAVE

SINON

DEBUT

SI maitre_emetteur ALORS

DEBUT

cpt:=cpt-1; P:=P+1;

TANT_QUE cpt>0 ET NON arbitr_perdue FAIRE

DEBUT

SO:=bufo[F]; cpt:=cpt-1; P:=F+1;

TANT_QUE NON transmis FAIRE RIEN

1

FINA

FIN:

SINON ( maitre recepteur }

DEBUT

P=Fbufi;

TANT_QUE cpt>0 ET NON arbitr_perdue FAIRE

DEBUT

I TANT_QUE NON transmis FAIRE RIEN

| bufi[P]:=S0; P:=P+1; cpt:=cpt-1;

FIN;

1

FIN;

Deconnexion;

SI arbitr_perdue ALORS P=FFH

SINON P=0

FIN;

```

PROCEDURE: ITI2C;

| ESCLAVE;

1

FIN#

FINE

DEBUT

FINA

```

PROCEDURE: ESCLAVE;

DEBUT

SI esclave_recepteur ALORS

1

DEBUT

CAS P

| =80H : f^:=S0; P:=P+1; SI f^<>0 ALORS P:=P+1;

=81H : f^:=S0; SI f^<>numpool ALORS deconnexion

SINON P:=P+1;

=82H : Adr_recept:=S0; P:=bufi; cpt:=0;

AUTRES: bufi[P]:=S0; P:=P+1; cpt:=cpt+1;

1

SI bus_occupe=FAUX ALORS P:=0;

1

FIN;

FIN;

SINON

```

TANT\_QUE NON transmis FAIRE RIEN

DEBUT { esclave emetteur }

TANT\_QUE bus\_occupe FAIRE

| SO:=bufo[P]; P:=P+1;

P:=buf0;

DEBUT

1

FIN;

### III. DESCRIPTION MATERIELLE

# III.1. Extrait du cahier des charges [ILL 82]

Le cahier des charges concernant la partie acquisition de données de l'expérience D20 spécifie:

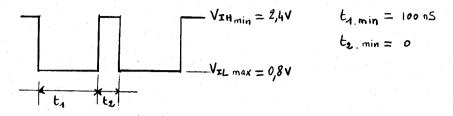

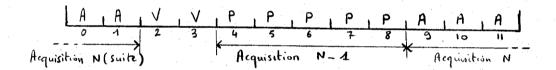

- 1600 voies individuelles de comptage ayant un temps mort maximum entre deux évènements de 1  $\mu$ S, et une capacité de 106 évènements par voies.

- Possibilité de "multiscaling" (Incrémentation dans différentes tranches de temps) et 100 zones disponibles.

- "Multiscaling synchronisant un dispositif externe ou synchronisable par un dispositif externe.

- Tranches de temps les plus faibles possible \le 10 mS.

- Temps mort entre 2 tranches le plus faible possible.

- Possibilité de fenêtrage à l'intérieur d'une tranche.

- Visualisation temps réel en cours de comptage des spectres contenus dans le système d'acquisition.

- Transfert vers le calculateur pilotant l'expérience en mode DMA.

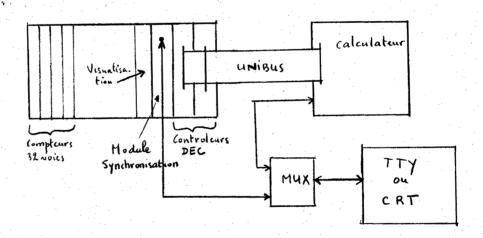

- Système pilotable par calculateur "Digital Equipment Corporation" ayant un Unibus ou QBUS (PDP11, VAX) par l'intermédiaire des contrôleurs du même constructeur standardisés à l'ILL.

Malheureusement en raison de problèmes techniques liés à la construction du multidétecteur, provisoirement le nombre de voies a été réduit à 128.

Par contre toute l'architecture exposée dans les chapitres suivants reste valable et justifiée.

## III.2. Description des modules

Face à ce cahier des charges, nous avons décidé de réaliser 3 types de modules:

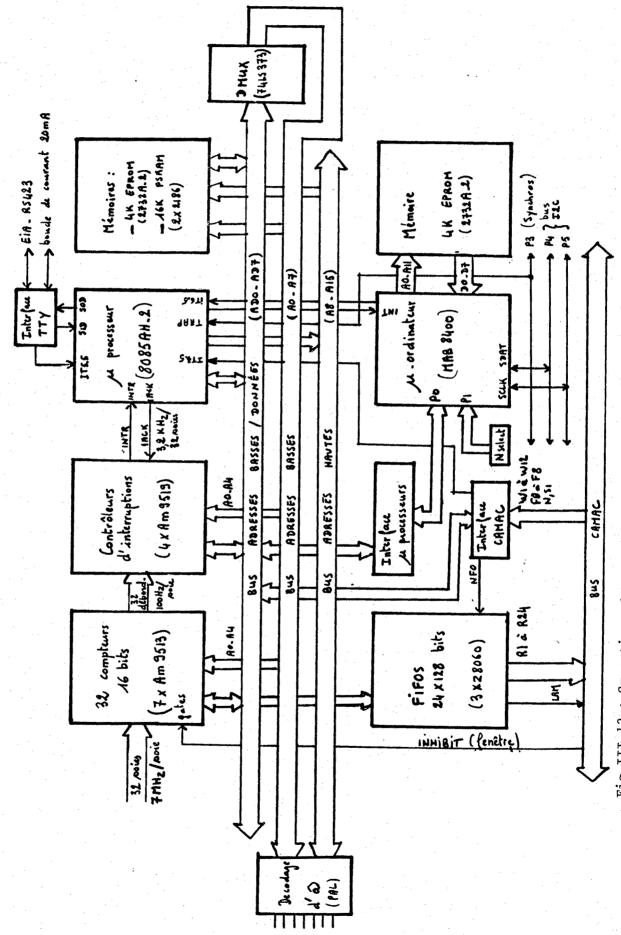

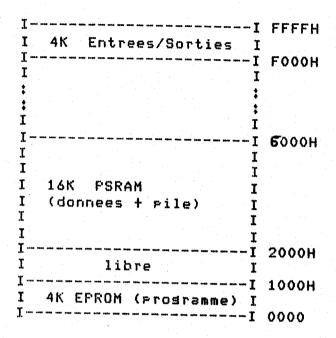

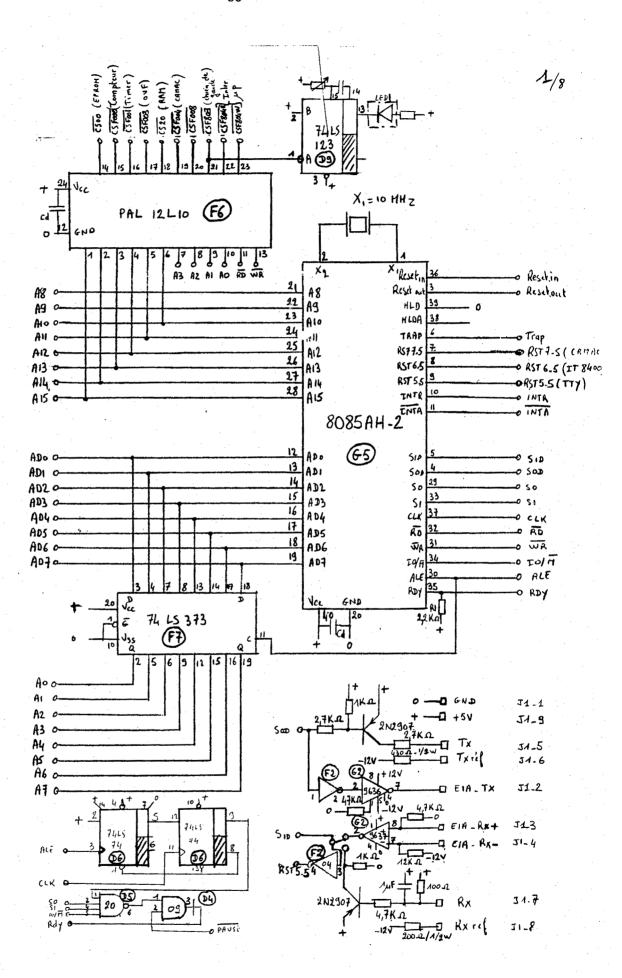

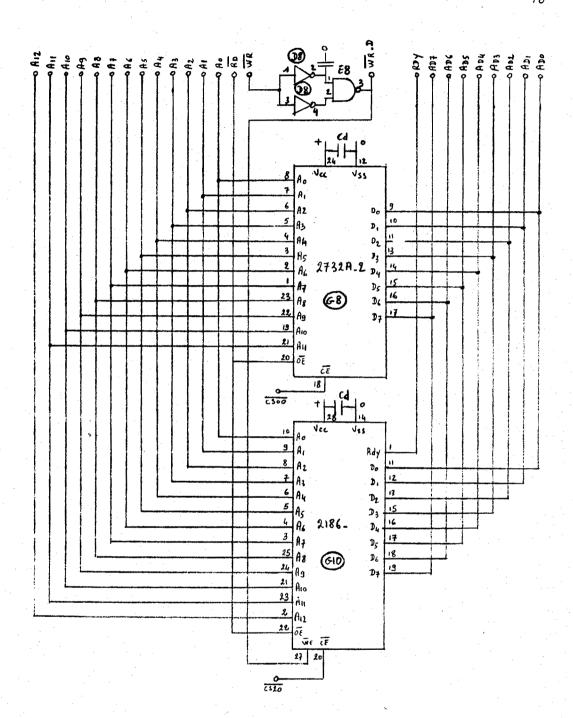

- Compteurs 32 voies/24 bits: En analysant les circuits disponibles sur le marché nous avons opté pour les circuits compteurs/temporisateurs d'AMD (Am 9513) qui comportent par CI, 5 compteurs de 16 bits, doublés de 5 registres de sauvegarde. Les dépassements de ces compteurs sont géré par des circuits de gestion d'interruption (Am 9519). Pour la gestion de cette carte nous avons mis un microprocesseur 8 bits d'Intel 8085, accompagné de 4K d'EPROM pour le programme et 16K de RAM pour les spectres, données et pile. Enfin pour transférer en mode DMA nous avons choisi de mettre des circuits FIFO de Zilog (Z8060). Tous ces circuits seront décrits plus précisement dans le chapitre suivant.

Ce choix réalisé nous avons décidé en raison des taux d'occupation de réaliser des modules compteurs gérant 32 voies chacun.

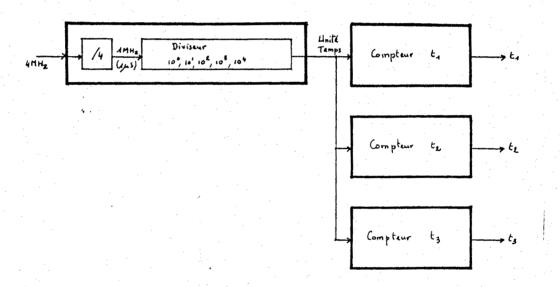

- Synchronisation: Pour synchroniser les modules compteurs 32 voies et également pour gérer les temps, il nous a fallu développer un autre module. Ce module est architecturé autour des mêmes circuits et compte un circuit Am 9513 fonctionnant en temporisateur et un second Am 9513 afin d'avoir 3 voies de comptage supplémentaires pour des dispositifs externes. Il compte également un CI Am 9519 pour la gestion des dépassements, ainsi que des FIFO (Z8060) pour les transferts. Ce module est également géré par un μρ 8085 ayant 4K d'EPROM, et 8K de RAM.

- Visualisation: Le module visualisation est réalisé autour du même µp 8085 8K d'EPROM et 1,5K de RAM. La partie graphique est réalisée autour du circuit EFCIS EF9367 qui gère une mémoire image de 512x256x4 Ceci permet de faire de la couleur au niveau de gris, ou de la superposition de plans.

Tous ces modules sont connectés au réseau local par le bus I2C et comporten un microordinateur MAB8400 et 4K d'EPROM.

Préalablement il est nécessaire de consacrer quelques pages à la description des circuits entrant dans la conception des différents modules.

# III.3. Descriptions des circuits utilisés

# III.3.1. Compteur/Temporisateur Am 9513 AMD 80

Le circuit compteur/temporisateur Am 9513 est un circuit LSI permettant de travailler de différentes manières (comptages, séquencement, générateur de temps programmable).

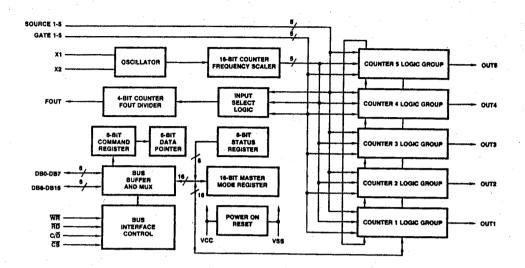

Ce circuit intégré comporte 5 groupes de compteurs de 16 bits pouvant être contrôlés à la fois par matériel et par logiciel (Fig. III.l.)

Fig.III.1.: Architecture interne du circuit compteur Am 9513.

Le comptage peut s'effectuer en incrémentation ou décrémentation aussi bien en binaire qu'en BCD.

Le contenu de chaque compteur peut être lu au vol sans déranger le comptage.

Les compteurs peuvent être cascadés internement formant ainsi un compteur jusqu'à 80 bits.

Il se connecte directement sur un bus de up 8 bits ou 16 bits.

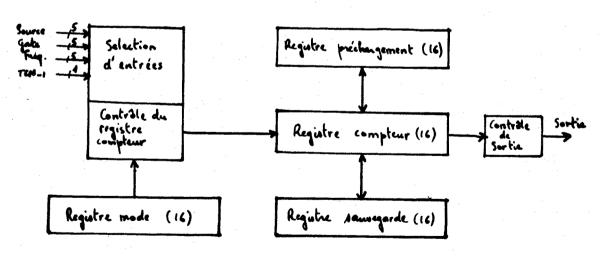

Fig.III.2.: Architecture d'un groupe de compteurs.

Comme on le voit sur la figure III.2. chaque groupe de compteur comporte les registres suivants:

- Le registre compteur

- Le registre de sauvegarde (Hold), qui permet entre autre la lecture au vol sans influencer le comptage.

- Le registre de préchargement (Load), qui permet de précharger le registre compteur:

- a. En mode compteur il est mis à 'o' et le registre compteur fonctionne en incrémentation.

- b. En mode temporisateur il est chargé par le temps de comptage et le registre compteur fonctionne en décrémentation.

- Le registre mode: définit le mode de fonctionnement du groupe (source de comptage, binaire ou BCD, Incrémentation ou décrémentation, unique ou répétitif, type de déclenchement du début de comptage).

La complexité de ce circuit permet de travailler d'une vingtaine de façons différentes. Sur notre application nous n'en utiliserons que 4 qui seront décrites dans la suite de ce mémoire.

Sur le bus up ce circuit ne représente que deux registres:

- Commande et état: qui sert à commander le démarrage, arrêt, etc..des compteurs. De plus il sert à positionner le pointeur des registres internes. En effet, on accède aux registres internes par un adressage indirect autoincrémenté.

- Données: écriture et lecture des données.

Deux commandes nous serons particulièrement utiles par la suite:

- "Disarm and Save": Qui désarme les compteurs et transfère leurs contenu dans les registres respectifs de sauvegarde.

- "Arm and Load": Qui transfère les contenus des registres de chargements dans les compteurs respectifs et démarre le comptage. Si les registres de chargements sont à 0000H, cette commande correspond à une remise à zéro.

Ces deux commandes permettent avec seulement deux accès au circuit, donc dans un temps très court:

- d'arrêter le comptage

- de sauvegarder les valeurs

- de remettre à zéro les compteurs

- de redémarrer un comptage

# III.3.2. Gestionnaire d'interruptions Am 9519 AMD 80

Le circuit gestionnaire d'interruption Am 9519 est un circuit LSI qui gère 8 interruptions et qui est capable de générer pour chacune d'elle une réponse programmée allant jusqu'à 4 octets. Ces circuits sont cascadables entre eux. Ils peuvent se connecter simplement à tous les microprocesseurs classiques.

La priorité des interruptions peut être fixe ou rotative c'est-à-dire qu'une interruption venant d'être servie passe en priorité la plus basse. En mode fixe c'est l'interruption la plus basse (matériellement) qui sera servie.

Les interruptions sont masquables individuellement. On peut également choisir les niveaux actifs de chaque interruption.

### Fonctionnement:

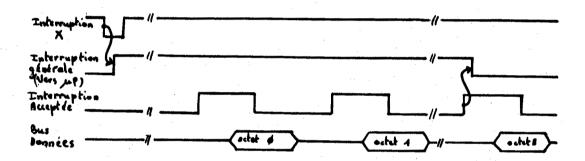

Lorsque une interruption se présente, elle est mémorisée. Si elle est autorisée le circuit génère une interruption générale vers le µp central. Cette interruption est reconnue par le µp qui répond par un premier signal interruption acceptée. Le contrôleur envoie sur le bus donnée le premier octet correspondant à la réponse. Le signal de demande d'interruption reste positionné, tant que le nombre d'octets de la répons initialisée n'a pas été lu et le processeur génére autant de signaux "interruption acceptée" (jusqu'à 4) (voir figure III.3.).

Figure III.3.: Diagramme de temps d'une reconnaissance d'interruption.

Pour le  $\mu p$  les octets de la réponse correspondent à des codes opérations qu'il éxécute au fur et à mesure.

Dans notre application le nombre d'octets est initialisé à 3. Ces octets correspondent à la génération d'un vecteur pour le branchement au sous programme d'interruption correspondant (CALL VECTX).

Comme pour le circuit précédent (Am 9513) le circuit Am 9519 ne représente que deux adresses sur le bus: commande/état, données. Les registres internes sont également adressables indirectement.

# III.3.3. Microprocesseur 8085 [INT 78]

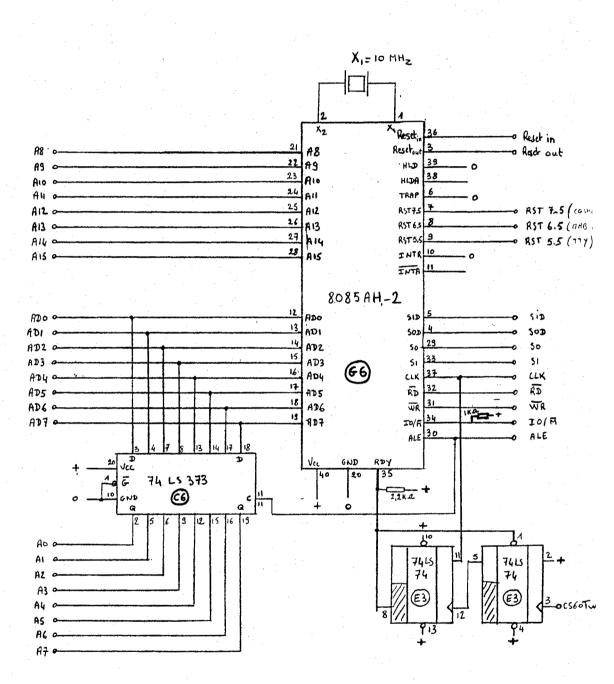

Le µp central est un 8085 de Intel. Il a été choisi pour cette application en raison de son implantation antérieure à l'ILL et de la possession d'un système de développement, mais également pour sa facilité d'implantation sur les modules.

En effet, sans être un monochip il ne nécéssite pas de circuits supplémentaires excepté les mémoires.

#### Il a les caractéristiques suivantes:

- Bus synchrone de 8 bits multiplexé (adresses basses, données). Bus adresses de 16 bits.

- Espace entrée/sortie séparé. Les périphériques ne font pas partie de la mémoire, mais sont séparés. Ils sont accessibles par des instructions spécifiques (IN, OUT). 256 registres périphériques peuvent être connectés. La sélection est assurée par un signal IO/M.

Si IO/M = o ALORS PO adresse la mémoire SINON PO adresse un périphérique (adresses hautes = adresses basses)

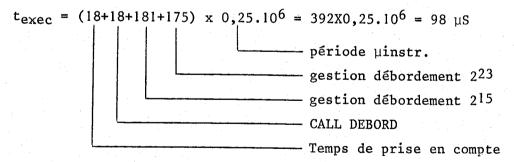

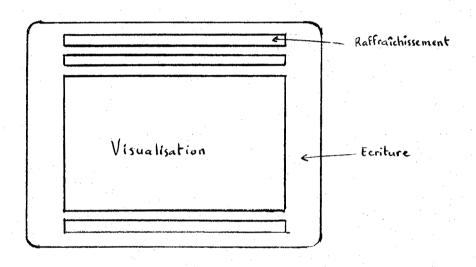

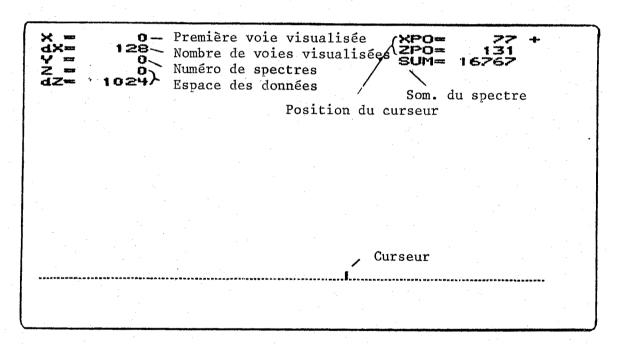

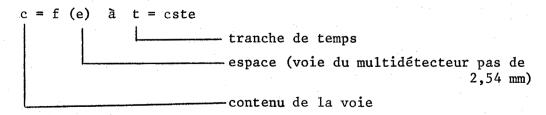

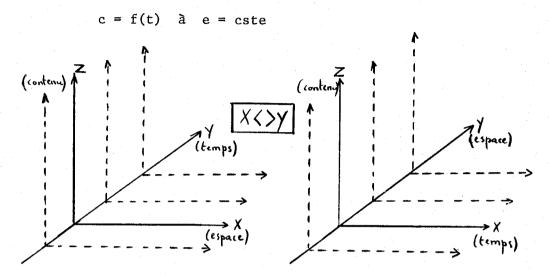

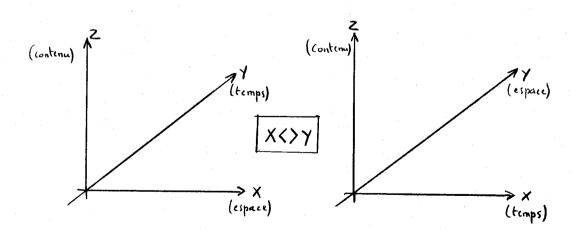

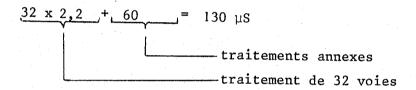

Cette philosophie présente l'inconvénient de restreindre considérablement le jeu des instructions pour les périphériques. Pour cette raison nous n'utiliserons pas cette possibilité et les circuits périphériques feront partie de l'espace mémoire et seront adressés comme tel.