# Predictability of just in time compilation Adnan Bouakaz

# ▶ To cite this version:

Adnan Bouakaz. Predictability of just in time compilation. Performance [cs.PF]. 2010. dumas-00530654

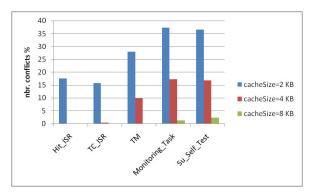

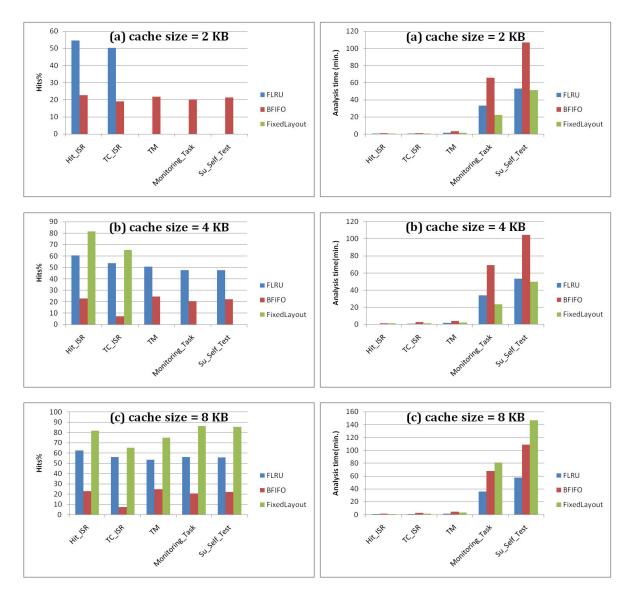

# HAL Id: dumas-00530654 https://dumas.ccsd.cnrs.fr/dumas-00530654

Submitted on 29 Oct 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# PREDICTABILITY OF JUST IN TIME COMPILATION

Adnan Bouakaz

Supervisors: Isabelle Puaut, Erven Rohou IRISA, ALF project

Research Master's degree in Computer Science

June 2010

# Contents

| $\mathbf{JIT}$ | Compilation & WCET Estimation                                                                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1            | Virtual Machines                                                                                                    | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.2            | JIT Compilation                                                                                                     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.3            | WCET Estimation Methods                                                                                             | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.4            | Predictability of HLL VMs & JIT Compilation                                                                         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pre            | dictability of the JIT Compiler Launching                                                                           | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1            | Background                                                                                                          | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.2            |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.3            |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.4            | •                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.5            |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.6            | •                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Exp            | perimental Results                                                                                                  | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

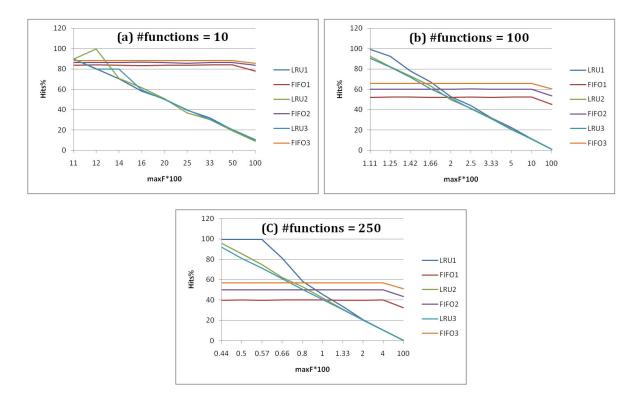

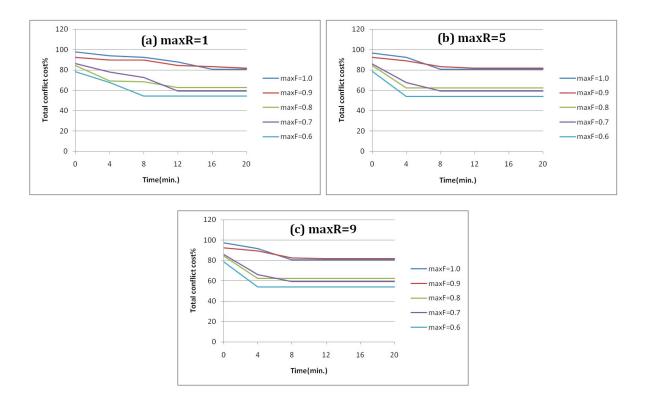

| 3.1            | Average Case Performance                                                                                            | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.2            |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3            |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.4            |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                | 1.1<br>1.2<br>1.3<br>1.4<br><b>Pre</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br><b>Exp</b><br>3.1<br>3.2<br>3.3 | 1.2       JIT Compilation         1.3       WCET Estimation Methods         1.4       Predictability of HLL VMs & JIT Compilation         Predictability of the JIT Compiler Launching         2.1       Background         2.2       Problem Statement and Assumptions         2.3       Fixed-Size Blocks with LRU System         2.4       Binary Buddy with LRU System         2.5       BFIFO System         2.6       Fixed Layout System         2.6       Fixed Layout System         3.1       Average Case Performance         3.2       Conflicts Determination         3.3       Cache Analysis |

# Introduction

The productivity of embedded software development is limited by the high fragmentation of hardware platforms. To alleviate this problem and to allow an efficient execution of applications on a large spectrum of hardware platforms, the computer science community has to invent a new form of application portability that will replace traditional binary compatibility. Virtualization has become an important tool in computer science; and virtual machines are used in a number of subdisciplines ranging from operating systems to processor architecture. The processor virtualization can be used to address the portability problem.

While the traditional compilation flow consists of compiling program source code into binary objects that can natively executed on a given processor, processor virtualization splits that flow in two parts: the first part consists of compiling the program source code into processor-independent bytecode representation; the second part provides an execution platform that can run this bytecode in a given processor. The second part is done by a virtual machine interpreting the bytecode or by just-in-time (JIT) compiling the bytecodes of a method at run-time in order to improve the execution performance.

Many applications feature real-time system requirements. The success of real-time systems relies upon their capability of producing functionally correct results within defined timing constraints. To validate these constraints, most scheduling algorithms assume that the worst-case execution time (WCET) estimation of each task is already known. The WCET of a task is the longest time it takes when it is considered in isolation. Sophisticated techniques are used in static WCET estimation (e.g. to model caches) to achieve both safe and tight estimation.

Our work aims at recombining the two domains, i.e. using the JIT compilation in realtime systems. This is an ambitious goal which requires introducing the deterministic in many non-deterministic features, e.g. bound the compilation time and the overhead caused by the dynamic management of the compiled code cache, etc. Due to the limited time of the internship, this report represents a first attempt to such combination. To obtain the WCET of a program, we have to add the compilation time to the execution time because the two phases are now mixed. Therefore, one needs to know statically how many times in the worst case a function will be compiled. It may be seemed a simple job, but if we consider a resource constraint as the limited memory size and the advanced techniques used in JIT compilation, things will be nasty. We suppose that a function is compiled at the first time it is used, and its compiled code is cached in limited size software cache. Our objective is to find an appropriate structure cache and replacement policy which reduce the overhead of compilation in the worst case. This will be a static analysis due to the safety factor as we will see later.

The rest of the document is organized as follows: Chapter 1 introduces the notions of JIT compilation and WCET estimation. In Chapter 2, we propose a solution to the abovementioned problem. Three cache management systems and their analyses are proposed in this chapter. Finally, some results of the analyses are presented in the third chapter.

# Chapter 1

# JIT Compilation & WCET Estimation

This chapter introduce two largely different domains. First, the benefits of *virtualization* and JIT compilation are listed in  $\S1.1$  and  $\S1.2$ ; then a brief survey on WCET estimation methods is presented in  $\S1.3$ . We conclude the chapter by asking a relevant question: What is needed to recombine the two domains to exploit their respective advantages?

# 1.1 Virtual Machines

Although nowadays computer systems are very complex, they continue to evolve. They are designed as hierarchies of different levels of abstraction separated by well-defined interfaces. Each abstraction hides a large amount of implementation details. In [31], we can find examples of such abstractions. For instance, computer's instruction set architecture (ISA) is a nice example of the well-defined interfaces.

Unfortunately, subsystems and components designed for one interface will not work with those designed for another (i.e. an *interoperability* problem). Virtualization provides a way to getting around such problems. Virtualizing a system or component (such as a processor, memory ...) at a given abstraction level maps its interface and visible resources onto the interface and resources of an underlying, possibly different, real system. Virtualization goals are not necessarily those of abstraction, i.e. simplifying or hiding details. It also provides *Software compatibility*: the virtual machine (VM) provides a compatible abstraction so that all software written for it will run on it, and *Isolation*: the VM abstraction isolates the software running in the VM from other VMs and real machines. To implement a VM, developers add a software layer to a real machine to support the desired architecture. There are two kinds of virtual machines [31]:

- System virtual machines: A system VM provides a complete environment in which an operating system and many processes of multiple users can coexist (e.g. Virtual PC in which a Windows system runs on a Macintosh platform). So, many isolated guest operating system environments can run on the same host hardware platform.

- **Process virtual machines:** A process VM provides a virtual ABI (Application Binary Interface) or API (Application Programming Interface) environment for user applications. Process VMs can offer replication, emulation and optimization. A key objective for process VMs is the cross-platform portability. Full cross-platform portability may be achieved by designing a process VM as a part of an overall high-level language (HLL)

application development environment. The resulting HLL VM does not directly correspond to any real platform; rather, it is designed for ease of portability and to match the features of a given HLL or set of HLLs. In this report, we are interested in HLL VMs only.

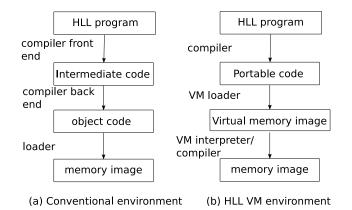

Figure 1.1: HLL environments

Figure 1.1 shows the difference between a conventional platform-specific compilation environment and an HLL VM environment. In a conventional system, a compiler front end generates intermediate code that is used by a code generator to generate a binary containing machine code for a specific ISA and operating system. The compiler front end of an HLL VM generates abstract machine code (called *bytecode*) in a virtual ISA that specifies the VM's interface. This code can be distributed for execution on different platforms (*portable* code). Each host platform must implement a VM able of loading and executing the virtual ISA.

As examples of HLL VMs, there are the Sun Microsystems Java VM architecture  $(JVM)^1$ and the Microsoft Common Language Infrastructure  $(CLI)^2$ . In both VMs, the ISAs are stackbased to eliminate register requirements and use an abstract data specification and memory model that supports secure object-oriented programming. There is not a big difference between the JVM and the Microsoft CLI specification, therefore Java is used as an example in the following sections.

#### 1.1.1 Different Types of JVM Implementations

The specification of the JVM is detailed in [19] without introducing the implementation aspects. The early JREs (Java runtime environments) executed Java programs by interpreting the bytecodes. So, ignoring exceptions, the inner loop of the JVM execution is:

do {

Fetches the next bytecode to execute and decodes it. If (operands) fetch operands. Execute the action for the opcode. } while (there is more to do)

The advantage of this approach is its simplicity; and the drawback is its modest performance. Addressing the performance gap with languages such as C or C++ means developing

<sup>&</sup>lt;sup>1</sup>http://java.sun.com/docs/books/jvms/

<sup>&</sup>lt;sup>2</sup>http://www.ecma-international.org/publications/standards/Ecma-335.htm

native code compilation for the Java platform in such a way the portability is not sacrificed. The first technique to explore is the *Ahead* of time translation (AOT). The principle idea is to translate all program bytecodes to machine code before execution. A big challenge of such technique is the dynamic class loading. A class cannot be loaded until the executing code makes a reference to that class. Because AOT occurs before the program executes, the compiler cannot make any assumptions about which classes have been loaded.

Another technique is the just-in time (JIT) compilation in which the first time a method is called it is translated into object code (see  $\S1.2$ ). We can find in [21] a detailed comparison between the AOT and the JIT compilation techniques.

The fourth technique is the hardware VM: a processor that implements the JVM instruction set. As an example, the Java optimized processor (JOP) [30]. JOP is a stack computer with its own instruction set, called microcode. Java bytecodes are translated into microcode instructions or sequences of microcode in hardware. This technique removes the overhead of decoding instructions in software. It does not, however, address the problem of portable execution on existing processors.

## **1.2 JIT Compilation**

Interpreting bytecodes is slow. Performing compilation prior to runtime and loading the program as native code would eliminate the portability and security of Java programs. On the other hand, compiling at runtime preserves these important properties. The program can still be distributed in platform-independent class files, and the bytecodes can still be verified prior to compilation. So unlike binary dynamic compilation, the process does not start with already compiled code but with bytecode. Both JIT and binary dynamic compilations have to manage a *compiled code cache*. There is a comparison between those two techniques in [8].

Unlike a static compiler, the compiling procedure is not entirely separated from the executing one in a JIT compiler. We can find in [36] a design of a Java JIT compiler. For a *mono-processor* architecture, the JVM includes four main components: class loader and linker, garbage collector, thread manager and a JIT compiler. For presentation clarity, we separate the JIT compiler from the JVM, so there are three states at runtime: JVM state, JIT compiling state and native code running state.

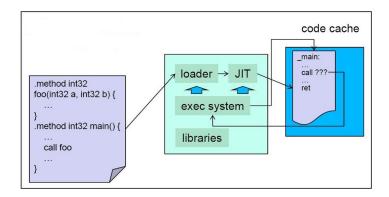

The state change in the JVM with a JIT compiler can be described as follows (Figure 1.2): at the beginning of the execution, the running state is in JVM. JVM loads and links the class file to be executed, and initializes the running environment. Before executing a method, JVM judges if the method has been translated into native code. If not, JVM calls the JIT compiler and the running state is changed into JIT compiling state. For translating a JVM method calling instruction, the JIT compiler must generate a native instruction which calls itself (a *trampoline*) to translate the Java method into native method. For some functions performed by the JVM (e.g. garbage collector), the JIT compiler should generate the native instructions which invoke them.

### 1.2.1 Challenges in JIT compilation

Although platform neutrality is maintained with JIT compilation, it comes at a price. Because compilation happens at the same time as program execution, the time it takes to compile code is added to the program's running time. Therefore, compilation speed is crucial. This is a very different situation from that facing a traditional, static compiler. To minimize overhead,

Figure 1.2: The JVM's state change

we can avoid compiling a method until it is certain that it will be executed. Compared to traditional static compilers, JIT compilers perform the same basic task of generating native code, but at much faster rate. The challenge for a JIT compiler is to find ways to generate efficient code without incurring the expense of traditional optimization techniques.

In many compilers, constructing an intermediate representation (IR) is a standard process. The bytecodes can be the IR for the JIT compiler. However, rather than treating bytecodes as literal descriptions of the code to be executed, a JIT can use them as implicit encodings of expressions. There are three major issues associated with transforming bytecodes directly into efficient machine instructions:

- The use of the operand stack constrains the order of evaluation specified by the bytecodes. More efficient orderings could be possible with a register-based processor.

- The best choice of machine instruction for a particular bytecode may depend on how a result of that bytecode is used. Indeed, some bytecodes are best translated to machine instructions in combination with the bytecodes that use their results.

- The bytecodes may include redundant operations.

More details about the JIT compilation process may be found in [7].

#### 1.2.2 Optimization in JIT compilers

Current JIT compilers can substantially improve performance, and future JVM implementation will use more advanced techniques to realize further performance gains [7]:

#### Adaptive optimization

One would like to tailor how to compile a method to the amount of time the program actually spends in that method. A dynamic compiler can observe the program as it runs (*profiling*) and optimize the most frequently executed models. A simple example is deciding when to compile based on observed execution frequencies. Recompiling based on observed behavior is a form of adaptive optimization. In adaptively optimization system, initial executions of a method either are interpreted or use a simple fast compiler. The code is self-monitoring, using execution counters, to detect hot spots. When a method is found worthy of optimization, the system can spend more time on its compilation.

This approach uses two dynamic compilers, a fast non-optimizing compiler and a second optimizing compiler. The authors of [17] discuss the utility of off-line profile information to decide which compiler to use initially. They developed an annotation framework to communicate that information with the JIT compiler. Another work in [18] presents a study of whether side-effect information collected off-line improves performance in JIT compilers.

#### Adaptive inlining

Inlining methods (replacing calls with the actual code of the called methods) is an important optimization in any program with a high call density and small methods. The use of virtual calls in Java defeats traditional inlining techniques, because many target methods may exist for a virtual call. A dynamic compiler can inline even a virtual call with more potential targets. The runtime system can note call sites which invoke the same method repeatedly. The compiler can also emit specialized versions of the method.

### **1.3 WCET Estimation Methods**

Unfortunately, HLL VMs are not widespread in real-time systems for a number of significant reasons (see \$1.4) which mainly concern their unability of validating timing constraints. But, they remain a target solution for the problem of the fragmentation of platforms for embedded systems. Indeed, the bytecode is an effective deployment format for embedded systems and so for real-time system [4].

The success of real-time systems relies upon their capability of producing functionally correct results within defined timing constraints. A *hard* real-time system is a system where a failure in the temporal domain will cause the system to fail. A *soft* real-time system is a system that will fulfill its mission even if deadlines are missed occasionally, but it should in normal operation not miss any deadline.

In a hard real-time system, there must be a guarantee that it does not miss any deadline in all situations. In order to achieve this, it is of vital importance to know the Worst-Case Execution Time (WCET) of each task. Unfortunately, it is not possible, in general, to obtain upper bounds on execution times for programs, unless we use a restricted form of programming which guarantees that programs always terminate; and which is the case in real-time systems.

The two main criteria for evaluating a WCET estimation method are: *safety* (does it produce upper bounds of execution times or not?) and *precision* (are the upper bounds close to the actual WCET?) In this section, the two main families of methods to bound the WCET of a task are presented [34].

#### 1.3.1 Static Methods

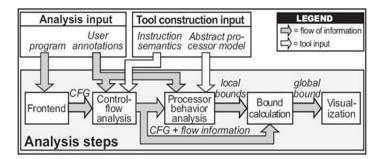

This class of methods does not rely on executing code on real hardware, but it analyzes the source code and/or the final executable, combines it with some model of the system's hardware, and obtains upper bounds from this combination. In this report, we are especially interested in source code analysis because we try to focus in the impact of virtualization and JIT compilation on the WCET estimation; and it is obvious that there is no generated object code for the whole task in a JIT compilation. The essential steps of the static analysis are depicted in Figure 1.3.

Figure 1.3: Core components of a timing-analysis tool

The input of such a method is a source code and some user annotations. The annotation of tasks, with information available from the developer, is a generic technique to supply information that the tool needs; e.g. ranges for the input values of the task, loop bounds, shapes of nested loops... The steps are:

#### Front end

The mostly used program representation is the control flow graph (CFG). This step aims at constructing it. Problems in such a construction are created by dynamic jumps and calls with computed target address. Dynamic calls occur in source code in the form of calls through function pointers and calls to virtual functions (which are a common situation in object-oriented programs).

#### Control Flow analysis (CFA, high-level analysis)

The purpose of CFA is to gather information about possible execution paths. The input of flow analysis consists of a task representation (e.g. CFG and call graph) and possibly additional information derived from annotations or by a value analysis. A value analysis is a static program analysis which aims at computing ranges for the values in the processor registers and local variables at every program point (it may be just sound approximations). This analysis is useful to predict the cache behavior, to determine loop bounds, and to detect infeasible paths. Indeed, some paths in the superset described by the CFG are infeasible, and it is better to eliminate them.

#### Processor behavior-analysis (low-level analysis)

Early approaches to the timing-analysis problem assumed context independence of the timing behavior; i.e. the execution time for individual instructions were independent from the execution history. So, if a task first executes a code snippet A (with an upper bound uA) and then a snippet B (with an upper bound uB), the worst-case bound for "A;B" is "uA + uB". This is no longer true for modern processors with caches and pipelines. The execution time of individual instructions may vary depending on the state of the processor in which they are executed.

To find precise execution time bounds for a given task, it is necessary to analyze what the occupancy state of these components is for all paths leading to the task's individual instructions. Processor-behavior analysis determines invariants about these occupancy states for the given task. Most approaches use data flow analysis and abstract interpretation [5]. Processor-behavior analysis needs a model of the architecture: an abstract processor model which is a simplified model that is conservative with respect to the processor timing behavior.

An analysis of the behavior of hardware caches yields to a tighter WCET of programs. The idea is to derive for each memory reference its worst-case behavior (hit/miss). To enforce safety, static cache analysis methods have to account for every possible cache contents, at every point in the execution, considering all paths to gather. Possible cache contents can be represented as sets of concrete cache states (*collecting semantics*) or by a more compact representation called abstract cache states (*Abstract Interpretation*) as we will detail in Chapter 2.

The complexity of the processor-behavior analysis subtask and the set of applicable methods critically depend on the complexity of the processor architecture. Most powerful microprocessors suffer from timing anomalies. Timing anomalies are contra-intuitive influences of the local execution time of one instruction on the global execution time of the whole task (see [20]).

#### **Bound calculation**

This step computes an upper bound of all execution times of the whole task, based on the flow and timing information derived in the previous phases. There are three main classes of bound calculation methods: path-based, structure-based, and techniques using implicit-path enumeration (IPET). We will detail here the IPET method which is the most used technique.

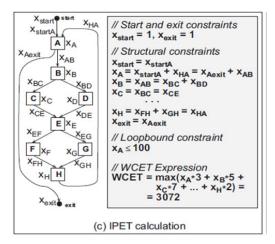

In IPET, program flow and basic-block execution time bounds are combined into sets of arithmetic constraints. Each basic block and program flow edge in the task is given a time coefficient  $(t_{entity})$  expressing the upper bound of the contribution of that entity to the total execution time, and a count variable  $(x_{entity})$ , corresponding to the number of times the entity is executed. An upper bound is determining by maximizing  $\sum_{i \in entities} x_i * t_i$ , where the execution count variables are subject to constraints reflecting the structure of the task and possible flows. Figure 1.4 shows an example of the application of the technique. The CFG of the task is depicted in the left side, and the ILP formulation in the right one. The variable  $x_A$  represents the number of execution of the basic block A, and  $x_{HA}$  is that of the edge from H to A. The constant 5 in the objective function corresponds to  $t_B, \ldots$

#### 1.3.2 Measurement-Based Methods

These methods execute the task or task parts on the given hardware or a simulator for some set of inputs. If you have the worst-case input for a given task, the precise determination of its WCET is an easy job. The problem is that determining such input is a very hard task. Exhaustively exploring all the input domain is too expensive as the number of cases to be explored is exponential w.r.t to the number of input variables. Measurements of a subset of all possible executions produce *estimates*, not safe bounds, if the subset is not guaranteed to contain the worst case.

Other approaches measure the execution time of basic blocks. The measured execution times are then combined and analyzed to produce non-safe estimates of the WCET. Thus, measurements replace the processor-behavior analysis used in static methods. The main problem of dynamic methods to bound the WCET might be *safety*. In this context, measurement-based methods are mainly used to validate static analysis methods.

Figure 1.4: IPET technique

The WCET estimation is difficult because of two things: history-based execution and dynamic features. The analysis of a branch predictor behavior is difficult. Indeed, the actual decision of the predictor is based on the precedent decisions; so the analysis of its behavior is more complex. The principle of "adaptive optimization" is not far from that of a branch predictor: the level of optimization is determined by the execution history. Dynamic features like dynamic jumps are a great source of imprecision in the WCET estimation. And for the lack of luck, languages such as Java are full of these features: virtual calls, dynamic class loading...

### 1.4 Predictability of HLL VMs & JIT Compilation

The use of an HLL VM like Java for real-time systems is justified by the need for software portability. The Java language's design includes some non-deterministic performance effects such as class loading and dynamic dispatching (§1.4.1). The need for performance has introduced the notion of JIT compilation in a VM; but it contains also non-deterministic effects (§1.4.2). To use these two techniques (Java and JIT compilation) in hard-real time systems, one need to predict statically their effects and calculate the WCET of a given task.

#### 1.4.1 Problems Caused by Java and other HLL VMs

We start first by describing some complexities appeared when using the object-oriented programming in general and the interpreted Java in particular. Object-oriented languages are not yet so widespread in real time systems. While simplifying for the programmer, they make WCET calculation of programs a harder task than for imperative programs. Some of those problems are listed in [12, 22]:

• Class loading: A Java-conformant JVM must delay loading a class until it is first referenced by a program. Loading a class can take a variable amount of time depending on the speed of the medium (disk or other) the class is loaded from, the class' size, and the overhead incurred by the class loaders themselves. The delay to load a class can

commonly be as high as 10 milliseconds. If tens or hundreds of classes need to be loaded, the loading time itself can cause a significant and possibly unexpected delay. Careful application design can be used to load all classes at application start-up, but this must be done manually because the Java language specification does not let the JVM perform this step early.

- **Dynamic binding:** This feature creates additional complexity, since it is not always known at compile time which method is going to execute. Even if one has knowledge of the WCET of all possible methods, dynamic binding may give a huge overestimation.

- Dynamic allocation and deallocation of memory: The time to allocate memory is not always predictable [12]. For deallocation, there are two mechanisms: explicit deallocation or automatic garbage collection. The garbage collector may interrupt the real-time system for an unpredictable time. However, many works consider it as a scheduling problem and not a WCET analysis problem [22, 30].

- Thread management: Standard Java provides no guarantees for thread scheduling or threads priorities. An application that must respond to events in a well-defined time has no way to ensure that another low-priority thread will not get scheduled in front of a high-priority thread. To compensate, a programmer would need to partition an application into a set of applications that the operating system can then run at different priorities. This partitioning would increase the overhead of these events and make communication between the events far more challenging.

Most approaches in the WCET estimation field for Java have simply assumed that dynamic dispatching features should be prohibited. In [14], E. Yu-shing et al. propose minimum annotations to address dynamic dispatching and so to reduce the overestimation of the WCET calculation. They use the user's knowledge about the application and the targets of a virtual call to increase the precision of the WCET estimation.

For JVMs, we find in [1] the proposal of a portable Java bytecode WCET estimation for Java bytecode (JBC) programs. The approach characterizes properties of a program that determine its WCET in a machine-independent, abstract way. Although the timing information is abstract, it represents the details that are necessary to port the information to a specific target platform and take into account its features (e.g. instruction pipeline or cache). After completion of the machine-independent WCET analysis, the WCET information is added to the Java class file of the program. Whenever the program is to be ported to a specific machine, the WCET information contained in the Java class file is augmented with machine-specific information (timing model) and evaluated for this machine. The models which are predictable and portable are: the hardware VM, the simple AOT translation and the interpreted VM because the compilation time of those models is bounded. So, the low-level analysis is portable to those different types of JBC execution.

#### 1.4.2 Problems Caused by the JIT Compilation

Authors in [1] consider JIT compilation unsuitable for real-time systems as the worst-case computation time has to include the time to compile the code which may be large and difficult to predict. Actually, most of the difficulties in the WCET estimation are raising form the dynamic properties of programs, adding another dynamic dimension (JIT compilation) makes

things much harder. Techniques such as "adaptive optimization" may be a great source of unpredictability of JIT compilation.

Our work is a first attempt to using JIT compilation in hard real-time systems; therefore we do not care about the problems caused by Java ( $\S1.4.1$ ) since those problems are tackled by many researches. There are many steps to achieve before using a JIT compiler in a real-time system; our work is only an answer of a first question: how many times a method will be compiled?

# Chapter 2

# Predictability of the JIT Compiler Launching

In this chapter, we present the work that is done during the internship. Using a JIT compiler in a real-time system is not an easy job as we have seen in the first chapter. Our goal is to incorporate the overhead caused by JIT compilation in the WCET estimation. When the static analysis of the program ends, each call to a function (or return) in the program has to be classified as always hit (whatever the execution path, the function is cached at this point) or not. In the negative case, the worst case compilation time must be incorporated in the worst-case execution time of the program. So, the objective is to answer statically the following question: how many times a function will be compiled? If the compiled code of a method stay in memory until the end of the program, then a function will be compiled at most one time.

An embedded system usually has hard resource constraints as a limited amount of memory, therefore we are obliged to use a limited memory zone which acts like a software cache to cache the compiled code. We have taken the following assumptions:

- We consider *mono-processor* and *mono-task* real-time systems.

- A limited compiled code cache. When there is no free place in the cache to hold the new compiled function, the binary code of others functions will be evicted from the cache. This mechanism will complicate the abovementioned question.

- A function must be systematically compiled (if it is not cached), but only when it is used.

- We do not allow advanced techniques of JIT compilation such as adaptive optimization.

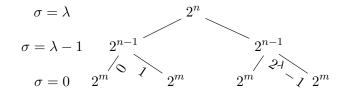

Our work is a proposition and an analysis of some cache management systems. The choice of a cache management system is guided by some real-time requirements. The analysis is essentially based on abstract interpretation, therefore we introduce data-flow analysis and abstract interpretation in Sections 1. In the rest of the chapter, we present three cache management systems: fixed-size blocks with LRU, binary buddy system with FIFO and a fixed-layout cache management system.

## 2.1 Background

The goal of this section is to introduce the needed information about data flow analysis and abstract interpretation. Those concepts are illustrated by examples related to cache analysis. This is an important step for presenting later a formal solution of the problem.

#### 2.1.1 Data Flow Analysis

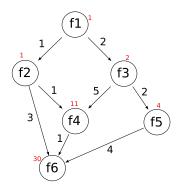

Data Flow Analysis (DFA) is the pre-execution process of ascertaining and collecting information about the possible run-time modification, preservation and usage of certain quantities in a computer program [13]. In our work the analysis is interprocedural and contextual, i.e. the analysis of a function depends on the context in which it is called. We represent a program as a control flow graph; a (CFG) per function and the set of CFGs are combined in an extended one by the call/return associations as depicted in Figure 2.1. There are three kinds of basic blocks: call, return and ordinary ones. An edge from a call node  $n_c$  to its successor  $n_s$  is replaced in the extended CFG by an edge from  $n_c$  to the entry node of the callee function and an edge from its return node to  $n_s$ .

Figure 2.1: An extended CFG

Many classical DFAs exist in literature [24, 13]: available expressions, reaching definitions, etc. Kam and Ullman [15] provided a generic framework called the monotone data flow analysis framework. At each point k of the program P (each node of the CFG), we put  $info_{in}(k)$  as the relevant information that is true on entry to the node, and  $info_{out}(k)$  as the relevant information that is true at exit. Those two values represent the information derived form every possible execution path which reach the node k (the Meet Over all Path (MOP) solution). The idea behind the monotone framework is that the relevant information can be modeled as a mathematics structure and the effect of a node on  $info_{in}(k)$  as a transfer function defined on the structure. We start first with a few mathematical facts (for more details see [2]).

**Example:** This example will be used to illustrate the concepts in following. In our work, the DFA is a software cache analysis. At each moment of the program execution, the cache holds some functions (this snapshot is called a concrete cache state). Let D the set of all possible concrete cache states. We try in this analysis to infer the information that for all possible paths, a function is always cached at a given node k (always hit). If we cannot decide, the compilation time must be incorporated in the WCET of the program.

#### Lattice Theory

**Poset:** A partially ordered set (poset) is a couple  $(B, \sqsubseteq)$  with B a set and  $\sqsubseteq$  a reflexive, antisymmetric and transitive relation on B. A poset  $(B, \sqsubseteq)$  verifies the ascending chain condition if for all ascending sequence  $b_0 \sqsubseteq b_1 \sqsubseteq \cdots b_n \sqsubseteq \cdots$  there exists an index k from which the sequence is stationary ( $\forall n \ge k : b_n = b_k$ ). A finite poset verifies the ascending chain condition. We often represent a poset as a Hasse diagram (a graph without the transitive relation). **Example:**  $(\wp(D), \subseteq)$  is a finite poset.

**Lattice:** A lattice is 4-tuple  $(B, \sqsubseteq, \sqcup, \sqcap)$  with:

- $(B, \sqsubseteq)$  a poset.

- $\square$  a binary least upper bound (*join*):

- $\forall b_1, b_2 \in B : b_1 \sqsubseteq b_1 \sqcup b_2 \land b_2 \sqsubseteq b_1 \sqcup b_2.$

- $\forall b_1, b_2, b_3 \in B : b_1 \sqsubseteq b_3 \land b_2 \sqsubseteq b_3 \Rightarrow b_1 \sqcup b_2 \sqsubseteq b_3.$

- $\sqcap$  a binary greatest lower bound (*meet*):

$$- \forall b_1, b_2 \in B : b_1 \sqcap b_2 \sqsubseteq b_1 \land b_1 \sqcap b_2 \sqsubseteq b_2.$$

$- \forall b_1, b_2, b_3 \in B : b_3 \sqsubseteq b_1 \land b_3 \sqsubseteq b_2 \Rightarrow b_3 \sqsubseteq b_1 \sqcap b_2.$

A poset with only the meet (resp. join) operation is called a meet-semilattice (resp. join-semilattice).

**Example:**  $(\wp(D), \subseteq, \cup, \cap)$  is a lattice.

**Complete lattice:** A complete lattice is a triple  $(B, \sqsubseteq, | |)$  with

- $(B, \sqsubseteq)$  a poset,

- | | a least upper bound: for all parts S of B,

$$- \forall b \in S : b \sqsubseteq \bigsqcup S$$

$$- \forall b_2 \in B : (\forall b_1 \in S : b_1 \sqsubseteq b_2) \Rightarrow \bigsqcup S \sqsubseteq b_2$$

All finite lattices are complete, and all complete lattices have a greatest element (the top element  $\top$ ) and a least element (the bottom element  $\perp$ ).

**Example:**  $(\wp(D), \subseteq, \bigcup)$  is a complete lattice with  $\phi$  as the least element and D as the greatest one. The meaning of  $\subseteq$  here is *more precise than*, so the more concrete cache states we have, the less information about the actual cache state we can extract. Therefore, if  $info_{in}(k) = D$  then everything is possible.

**Monotone function:** A function  $\psi : B_1 \longrightarrow B_2$  between posets  $(B_1, \sqsubseteq_1)$  and  $(B_2, \sqsubseteq_2)$  is monotone if  $\forall b_1, b_2 \in B_1 : b_1 \sqsubseteq_1 b_2 \Rightarrow \psi(b_1) \sqsubseteq_2 \psi(b_2)$ .

**Fixpoint:** Consider a monotone function  $\psi : B \longrightarrow B$  on a complete lattice  $(B, \sqsubseteq, \bigsqcup)$ . A *fixed point* of  $\psi$  is an element  $b \in B$  such that  $\psi(b) = b$ . The least fixpoint  $lfp(\psi)$  of  $\psi$  exists [32].

#### Monotone Framework

The relevant information at each node k is modeled by an element of a join-semilattice  $(B, \sqsubseteq)$  that has an element  $\top$  and which verifies the ascending chain condition (or by duality as a meet-semilattice). The *join* (least upper bound) operation represents the effect of information converging from paths. The effect of each node is modeled by an operation  $\psi_k$  on the semilattice. Because there are many different operations (an operation per node), we must form a monotone operation space  $\Psi$  associated with B which verifies three conditions:

- each  $\psi_k$  is in  $\Psi$  and it is monotone.

- $\Psi$  contains the identity function (because certain nodes have no effect).

- $\Psi$  is closed under composition of functions. This condition reflects the action of passing information through successive nodes.

So, a monotone framework consists of a complete lattice and a monotone operation space. A distributive framework is a monotone framework where:  $\forall \psi_k \in \Psi : \psi_k(b_1 \sqcup b_2) = \psi_k(b_1) \sqcup \psi_k(b_2)$ .

**Example:** Let  $\mathcal{F} = \{f_1, f_2, \ldots, f_n\}$  be the list of program functions. A cache update function:  $\delta: D \times \mathcal{F} \longrightarrow D$  describes the new cache state for a given cache state and a referenced function. The effect of an update function is determined by the cache management system (cache structure, replacement policy...). For a call node k (or a return one) which references the function  $f_i$ , we associate a function  $\psi_k = \Delta_i$  such that,  $\forall x \in \wp(D) : \Delta_i(x) = \{d' \in D/d' = \delta(d, f_i) \land d \in x\}$ . For an ordinary node  $\psi_k = id$ .

$\forall x, y \in \wp(D), \forall i : x \subseteq y \Leftrightarrow \Delta_i(x) \subseteq \Delta_i(y)$ . So,  $\Delta_i$  is a monotone function on  $(\wp(D), \subseteq, \bigcup)$ . The composition of monotone functions is a monotone function and if we take the composition closure then we will have a monotone operation space. In summary, we will have a distributive framework.

The Meet Over all Paths (MOP) solution is undecidable [13], and instead of the MOP solution we compute the MFP one (the maximum fixed point). They are equivalent when the framework is distributive. The problem is usually formulated as an equation system (see [24] for the overall pattern). The solution of this equation system is the least fixpoint (or the greatest one).

**Example:** For our example the equation system is:

$$info_{in}(k) = \begin{cases} \{\bar{d}\} & \text{if } k \in \text{init}(P) \\ \bigcup info_{out}(k')/(k',k) \in \text{flow}(P) & \text{else} \end{cases}$$

Such that:  $\overline{d}$  is the initial concrete cache state which contains the entry function.

$$info_{out}(k) = \begin{cases} info_{in}(k) & \text{if } k \text{ is neither a call block nor a return one} \\ \Delta_i(info_{in}(k))/f_i \text{ is the referenced} \\ \text{function by the node } k & \text{else} \end{cases}$$

Such that: init(P) is the entry nodes of the program and flow(P) is the control flow represented as a set of edges.

#### 2.1.2 Abstract Interpretation

Sometimes calculations on a complete lattice may be expensive or even uncomputable. Unfortunately this the case for the cache analysis; the concrete cache states domain D is huge and so more  $\wp(D)$ . We call the analysis developed in the previous example "the collecting semantics". The idea of approximating a program semantics corresponds to a restriction of the set of properties used to express the behavior of a program i.e. the restriction of  $\wp(D)$  to  $\overline{D}$  where  $\overline{D} \subseteq \wp(D)$ . Instead of representing properties in a concrete domain, one represents more abstract information in an abstract domain and which is the idea of abstract interpretation [5]. Abstract Interpretation is a formal method in static analysis used to determine statically (without executing the program) uncomputable properties of programs.

So, we have the concrete world represented by a complete lattice generally of the form  $(\wp(B), \subseteq, \bigcup)$ ; an abstract world modeled as a complete lattice  $(\widehat{B}, \sqsubseteq, \bigsqcup)$ . The relation between the two complete lattices is expressed by two monotone functions:

$$(\wp(B),\subseteq,\bigcup) \stackrel{\alpha}{\underset{\gamma}{\longleftrightarrow}} (\widehat{B},\sqsubseteq,\bigsqcup)$$

Where:

- $\alpha$  is an abstraction function,  $\alpha: \wp(B) \longrightarrow \widehat{B}$

- $\gamma$  is a concretisation function,  $\gamma: \widehat{B} \longrightarrow \wp(B)$

This relation explains the meaning of elements of  $\widehat{B}$  in terms of elements of  $\wp(B)$  and it is called a *Galois connection*.

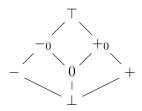

**Example:** A very famous example is the abstraction by signs [5]. The concrete world is  $(\wp(\mathbb{Z}), \subseteq, \bigcup)$  and the abstract world is represented by the lattice of signs depicted in Figure 2.2. As examples,  $\alpha(\{x \le 0/x \in \mathbb{Z}\}) = -_0$  and  $\gamma(0) = \{0\}$ . Operations, such as addition, can be defined on this lattice; e.g.  $0 \ plus + = +_0$ .

Figure 2.2: The sign lattice

To not lose safety by going back and forth between the two lattices, the two functions must verify the two following properties:

$$\forall x \in \wp(B) : x \subseteq \gamma \circ \alpha(x) \text{ and } \forall \hat{b} \in \widehat{B} : \alpha \circ \gamma(\hat{b}) \sqsubseteq \hat{b}$$

If  $\gamma$  is injective then  $\forall \hat{b} \in \widehat{B} : \alpha \circ \gamma(\hat{b}) = \hat{b}$ ; and we call the relation a *Galois insertion*.

**Function approximation:** For a monotone function  $\widehat{\psi} \in \widehat{B} \longrightarrow \widehat{B}$  and a function  $\psi \in \wp(B) \longrightarrow \wp(B), \widehat{\psi}$  is a correct approximation of  $\psi \Leftrightarrow \alpha \circ \psi \circ \gamma \sqsubseteq \widehat{\psi}$ . Hence,  $\alpha \circ \psi \circ \gamma$  is the best abstract function  $\widehat{\psi}$  and which verifies  $\alpha(lfp(\psi)) \sqsubseteq lfp(\widehat{\psi})$ .

You can find proofs and how we use the abstraction with a monotone framework in [24].

#### **Reduced Product**

Let us take two Galois connections:

$$(\wp(B),\subseteq,\bigcup) \xrightarrow{\alpha_1}_{\gamma_1} (\widehat{B}_1,\sqsubseteq_1,\bigsqcup_1) \text{ and } (\wp(B),\subseteq,\bigcup) \xrightarrow{\alpha_2}_{\gamma_2} (\widehat{B}_2,\sqsubseteq_2,\bigsqcup_2)$$

We can run the two analyses without any collaboration between them; but we can do better. The objective is to cooperate the two analyses to obtain information which is more precise than we can obtain with separated analyses. Because we have the same concrete domain, we can combine these two abstractions with a new connection:

$$(\wp(B),\subseteq,\bigcup) \xrightarrow{\bar{\alpha}}_{\bar{\gamma}} (\widehat{B}_1 \times \widehat{B}_2,\sqsubseteq,\bigsqcup)$$

Where:

$$\forall (\hat{b}_1, \hat{b}_2), (\hat{b}'_1, \hat{b}'_2) \in (\hat{B}_1 \times \hat{B}_2) : (\hat{b}_1, \hat{b}_2) \sqsubseteq (\hat{b}'_1, \hat{b}'_2) \Leftrightarrow \hat{b}_1 \sqsubseteq_1 \hat{b}'_1 \wedge \hat{b}_2 \sqsubseteq_2 \hat{b}'_2.$$

$$\forall x \in \wp(B) : \bar{\alpha}(x) = (\alpha_1(x), \alpha_2(x)) \text{ and } \forall (\hat{b}_1, \hat{b}_2) \in \hat{B}_1 \times \hat{B}_2 : \bar{\gamma}(\hat{b}_1, \hat{b}_2) = \gamma_1(\hat{b}_1) \cap \gamma_2(\hat{b}_2).$$

**Example**: If we combine the Galois insertion of signs which infers  $\hat{b}_1 = +$  (i.e.  $\gamma_1(\hat{b}_1) = \{n > 0\}$ ) with the Galois insertion of intervals which infers  $\hat{b}_2 = [-5, 2]$ , then we can refine  $\hat{b}_2$  to  $\hat{b}_2 = [0, 2] = \alpha_2(\gamma_1(\hat{b}_1) \cap \gamma_2(\hat{b}_2))$ .

In abstract interpretation, we call this concept *reduced product*. We define a reduction operator  $\rho$  which allows computations on a reduced product  $\rho(\hat{B}_1 \times \hat{B}_2)$ . It allows to combine efficiently and for free two correct approximations. If  $\hat{\psi}$  is an abstract function, then  $\rho \circ \hat{\psi} \circ \rho$  is a more precise version (but not the most precise).

# 2.2 Problem Statement and Assumptions

Three cache management systems are proposed in the rest of this chapter. Each one of them has its own advantages and drawbacks. A cache analysis is developed for each system. But, we present first the assumptions and constraints behind our propositions.

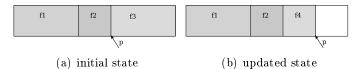

Unlike a hardware cache, a compiled code cache needs neither a fixed structure nor a fixed replacement policy. Indeed, the JIT compiler can switch statically (at a program starting) from a cache management method to another accordingly to the designer choice. Our objective is to find an appropriate predictable management system. The software cache management is similar to the dynamic storage allocation (DSA), except there is no release operation. The application can only request blocks to load the binary code of a function at a call or a return instruction (and we say that the function is referenced) if the function is not cached. If there

is not enough free place in the cache to hold the requested binary code, some functions will be evicted according to the replacement policy. Dynamic storage allocators have no replacement mechanism. They just throw a memory overflow exception when there is no available memory to serve a new request.

20

This similarity between software cache management and DSA allows us to adjust some techniques of DSA for our purposes. Several efficient implementations of dynamic storage allocator exist [35], but if we are interested in using them for real-time systems, one will have to take in consideration the predictability factor and not only the performance issues. In [28], Puaut provides a guideline to developers of real-time systems to decide whether they will use DSA or not in their systems. The paper gives the analytic worst-case of the routines (malloc/free) of a comprehensive panel of allocators. The assumptions behind those allocators are imposed by the real-time nature. We have adopt some of those assumptions:

- The algorithms allocate areas of real memory, i.e. no address translation nor paging.

- There is no block relocation. Indeed, although the block relocation mechanism has its own advantages, it is a time consuming process, therefore we avoid to use it in JIT compilation.

The requirements for a real-time software cache management system are:

- **Temporal predictability:** The JIT compiler must keep information about free memory blocks to serve new requests; and it has to perform some form of search to find a suitable free block. The WCET of this search must be constant or bounded. In terms of dynamic storage allocators; *Binary buddy systems* [26], *Half-fit* [25] and *TLSF* [23] have been considered as real-time allocators. We will take a glance on the binary buddy system because we have used it in our work, not the allocator but the idea behind it (see §2.4 and §2.5).

- Spatial predictability: Fragmentation is the inability to reuse memory that is free. Internal fragmentation is the result of rounding up the requested size to the closest predefined block size. External fragmentation result from breaking available memory into blocks. Two blocks can be recombined once they are free only if they are neighbors. Real-time systems have to operate over very long periods; and therefore, fragmentation causes a significant performance degradation. For dynamic storage allocators, the fragmentation is unpredictable for almost them except for Compact-Fit [6]. This allocator use the relocation mechanism which we avoid. So, we must be careful about fragmentation when we design the management system, because it can be the most important reason that makes a given management method better than another (see §3.3.1).

## 2.3 Fixed-Size Blocks with LRU System

The cache is divided into a set of fixed-size blocks. The block size BS is equal to the size of the largest binary code of all the program functions. Let  $\mathcal{F} = \{f_1, f_2, \ldots, f_n\}$  be the list of program functions.  $Size : \mathcal{F} \longrightarrow \mathbb{N}^+$  a function associates with each function  $f_i$  the size of its binary code  $Size(f_i) = s_i$ . So the size of a cache block will be  $BS = \max(s_1, s_2, \ldots, s_n)$ ; and the number of blocks will be  $NB = \lfloor \frac{C}{BS} \rfloor$  where C is the cache size. The replacement policy for this management system is the LRU (Least Recently Used) policy.

- Advantages: We can borrow the hardware cache analysis and apply it easily on software caches. This analysis is straightforward, fast and efficient.

- Drawbacks: The most significant drawback of this management system is internal fragmentation specially when the sizes of functions are heterogeneous. For each function  $f_i$ in the cache,  $(BS - s_i)$  memory units are wasted. In terms of external fragmentation,  $(C \mod BS)$  memory units are never exploited. Another drawback is that the implementation of LRU in the allocator is more time consuming than other policies (such as FIFO) because we must keep track of age of each function in the cache and searching always for the function with the greatest age.

In hardware cache analysis, a framework based on abstract interpretation [5] is often used. For LRU replacement policy, there are usually two analyses [9]. A must-analysis which determines a set of memory blocks (in our case, a set of functions) that *must* be in the cache at a given program point upon any execution. A may-analysis which determines all the functions that *may* be in the cache at a given program point. The must-cache information is used to derive safe information about cache *hits*, and may-cache analysis is used to safely predict cache *misses*.

In follow, we transpose the analysis of fully associative hardware caches with LRU replacement policy [9] to our case. Instead of a collecting semantics, we will build two abstract domains: a *Must* domain to infer information about always hits and a *May* domain to infer the information about always misses. This is a formal construction to ensure the correctness of the approximation and the termination of the analysis.

#### 2.3.1 Must Analysis

Let  $Age = \{0, 1, \ldots, NB - 1\}$  and  $Age_{\omega} = Age \cup \{\omega\}$  with the order  $\forall i \in Age : i < \omega$  (we can take  $\omega$  as NB). Let us take the abstract domain  $Must = \mathcal{F} \longrightarrow Age_{\omega}$  (We associate with each function an age in the software maintained function cache).

- $m_1, m_2 \in Must : m_1 \sqsubseteq_{must} m_2 \Leftrightarrow \forall f_i \in \mathcal{F} : m_1(f_i) \le m_2(f_i).$

- $(Must, \sqsubseteq_{must})$  is a poset.

- $m_1, m_2, m_3 \in Must: m_3 = m_1 \sqcup_{must} m_2 / \forall f_i \in \mathcal{F}: m_3(f_i) = \max(m_1(f_i), m_2(f_i)).$

- $m_1, m_2 \in Must; m_3 = m_1 \sqcap_{must} m_2 / \forall f_i \in \mathcal{F} : m_3(f_i) = \min(m_1(f_i), m_2(f_i)).$

$(Must, \sqsubseteq_{must}, \sqcup_{must}, \sqcap_{must})$  is a finite lattice and therefore  $(Must, \sqsubseteq_{must}, \bigsqcup_{must})$  is a complete one.

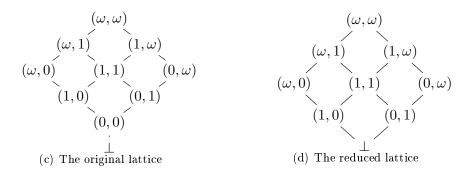

**Example:** For a cache with NB = 2 and  $|\mathcal{F}| = 2$ , we obtain the lattice in picture 2.3(c). An element  $(1, \omega)$  means that the maximal age of  $f_1$  is 1 and the maximal age of  $f_2$  is  $\omega$ .

Now, to apply the abstract interpretation we need a Galois connection:

$$(\wp(D),\subseteq,\bigcup) \xrightarrow[\gamma_1]{\alpha_1} (Must,\sqsubseteq_{must},\bigsqcup_{must})$$

We define the abstraction function  $\alpha_1$  as:

Figure 2.3: A lattice for an LRU cache

- $\alpha_1(\phi) = \bot$ . We extend (*Must*,  $\sqsubseteq_{must}$ ,  $\bigsqcup_{must}$ ) with the least element  $\bot$ .

- $\forall x \in \wp(D) : \alpha_1(x) = m \in Must/\forall f_i \in \mathcal{F} : m(f_i)$  = the maximal age of the function  $f_i$  in all concrete cache states in x.

For a concrete cache state, if  $f_i$  it has just been referenced, then the age of  $f_i$  is 0; and if  $f_i$  is not cached then the age will be  $\omega$ . So,  $\alpha_1(x)(f_i) = \omega$  means that  $f_i$  can be not cached, and  $\alpha_1(x)(f_i) = k$  means that  $f_i$  it will stay at least NB - k - 1 references (calls or returns) that are not in the abstract cache (or older than  $f_i$ ) for all paths reaching the concerned node. The meaning of  $\sqsubseteq_{must}$  is not "more precise" but "better than" in terms of hit information.

**Example:** Let  $x_0$  a set of concrete cache states.  $x_0$  contains two states:  $[f_1(0), \phi]$  and  $[f_1(1), f_2(0)]$  (f(a) means that the age of f is a). So,  $\alpha_1(x_0) = m_0/m_0(f_1) = 1 \land m_0(f_2) = \omega$ .

We define the concretisation function as:

- $\gamma_1(\perp) = \phi$ .

- $\forall m \in Must \setminus \{\bot\} : \gamma_1(m) = \{d \in D / \forall f_i \in \mathcal{F} : \text{age of } f_i \text{ in } d \leq m(f_i) \}.$

**Example:** For the previous example,  $\gamma_1(m_0) = \{d \in D | \text{age of } f_1 \text{ in } d \leq 1 \land \text{ age of } f_2 \text{ in } d \leq \omega \}$ . So,  $\gamma_1(m_0) = \{[f_1(0), \phi], [f_1(0), f_2(1)], [f_2(1), f_1(0)], [f_2(0), f_1(1)], [f_1(1), f_2(0)]\}$ .

$\gamma_1$  is not injective because in addition to  $\gamma_1(\perp) = \phi$  there are some  $m \in Must \setminus \{\perp\}$  such as  $\gamma_1(m) = \phi$  (e.g., if  $m(f_i) = 0$  and  $m(f_j) = 0$ ). From now, we suppose that  $|\mathcal{F}| \leq NB$ . Generally,

$$\forall m \in Must \setminus \{\bot\} : \gamma_1(m) = \phi \Leftrightarrow \exists 0 \le k < \omega : \sum_{m(f_i) \le k} 1 > k+1$$

In our analysis this case never happens, and if we eliminate those cases, then  $\gamma_1$  will be injective and the analysis is still sound because the reduced set is also a complete lattice. We can easily prove that if  $m_1$  is not valid then:  $\forall m_2 \in Must \setminus \{\bot\} : m_2 \sqsubseteq_{must} m_1 \Rightarrow m_2$  is also not valid. From now, our operations are on the reduced lattice.

**Example:** For the lattice of the previous example, the element (0,0) is not valid. The reduced lattice is depicted in Figure 2.3(d).

We have,  $\forall x \in \wp(D) : x \subseteq \gamma_1(\alpha_1(x))$ , and  $\forall m \in Must : m = \alpha_1(\gamma_1(m))$ . So, this abstraction is a correct approximation.

#### The access function

Let the function  $cl: \wp(D) \times \mathcal{F} \longrightarrow \{H, M, U\}$ .  $\{H, M, U\}$  is a join-semilattice (Figure 2.4). If  $x \in \wp(D) \setminus \{\phi\}$  then  $cl(x, f_i)$  describes the access type of a reference to  $f_i$  in a set of concrete states. So:

$$cl(x, f_i) = \begin{cases} \text{Hit } (\mathbf{H}) & \text{if } \forall d \in x : f_i \text{ is in } d \\ \text{Miss } (\mathbf{M}) & \text{if } \forall d \in x : f_i \text{ is not in } d \\ \text{Unclassified } (\mathbf{U}) & \text{otherwise} \end{cases}$$

The abstraction of the access function will be:  $\widehat{cl} = cl \circ \gamma_1$ . Let  $m \in Must \{ \perp \}$ ; if  $m(f_i) \neq \omega$ then it is a hit **(H)**, else it is an unclassified reference unless if  $\sum_{m(f_k)\neq\omega} 1 = NB$  and so it will be a miss **(M)**. This abstraction is exact. The only issue is if  $\widehat{cl}(m, f_i) = \mathbf{U}$  but  $cl(\gamma_1(m), f_i) = \mathbf{M}$ , but this is impossible, because  $\gamma_1(m)$  contains at least an element d where the age of  $f_i$  in d equals to NB - 1.

Figure 2.4: The access classification lattice

**Example:** Always using the same example,  $\widehat{cl}(m_0, f_2) = \mathbf{U} = cl(\gamma_1(m_0), f_2)$ .

#### Abstraction of the update function

For LRU, when a miss happens and there is no free place in the cache, the function with age equals to NB - 1 will be evicted, the inserted function will have the age equal to 0 and the age of all other function will be incremented by 1. If the access is a hit then the age of the referenced functions will be updated to 0 and functions with age less than the age of the referenced function will become older (ages incremented by 1).

As the theory of abstract interpretation says: the best abstraction of  $\Delta_i$  is  $\widehat{\Delta_i} = \alpha_1 \circ \Delta_i \circ \gamma_1$ . We are lucky since this specification can be written easily as an algorithm: Let  $m, m' \in Must \setminus \{\bot\}$  two abstract cache states such as  $m' = \widehat{\Delta_i}(m)$ , So:  $m'(f_i) = 0$  and

$$\begin{cases} m'(f_j) = m(f_j) + 1/m(f_j) < m(f_i) & \text{if } \widehat{cl}(m, f_i) = \mathbf{H} \\ m'(f_j) = m(f_j) + 1/m(f_j) \neq \omega & \text{if } \widehat{cl}(m, f_i) = \mathbf{M} \lor \widehat{cl}(m, f_i) = \mathbf{U} \end{cases}$$

If the reference to  $f_i$  is *unclassified*, and because of the existence of an element d in  $\gamma_1(m)$  such that age of  $f_i$  in d equals to NB - 1, then the effect of the update function is like when the access is a miss.

To conclude, the data-flow equations of the must-analysis will be: for each basic block k in the program P:

$$AC_{in}(k) = \begin{cases} \bar{m} & \text{if } k \in \text{init}(P) \\ \bigsqcup_{must} AC_{out}(k')/(k',k) \in \text{flow}(P) & \text{else} \end{cases}$$

Such that  $\bar{m} = \alpha_1(\{\bar{d}\})$  i.e.  $\forall f_i \in \mathcal{F} : \bar{m}(f_i) = 0$  if  $f_i$  is the entry function and  $\bar{m}(f_i) = \omega$  else.

$$AC_{out}(k) = \begin{cases} AC_{in}(k) & \text{if } k \text{ is not a call block nor a return one} \\ \widehat{\Delta_i}(AC_{in}(k))/f_i \text{ is the referenced} \\ \text{function in node } k & \text{else} \end{cases}$$

Finally, the termination and the correctness of this analysis are guaranteed by using the theory of abstract interpretation [5].

#### 2.3.2 May Analysis

The may-analysis is roughly dual to the must-analysis. Instead of taking the maximal age of a function, we take the minimal one. This analysis is used in [9] to predict misses in hardware caches. In our case, there are no timing anomalies, therefore we do not need for a may-analysis. But, we present it for two reasons: to explain easily the intuition behind the may-analysis which is used later in the analysis of an another management system (§2.5) and to explain also why the collaboration between the may-analysis and the must-analysis can be useful for some management systems and not for others.

Let us take the abstract domain  $May = \mathcal{F} \longrightarrow Age_{\omega}$ .

- $m_1, m_2 \in May : m_1 \sqsubseteq_{may} m_2 \Leftrightarrow \forall f_i \in \mathcal{F} : m_1(f_i) \ge m_2(f_i).$

- $m_1, m_2 \in May: m_3 = m_1 \sqcup_{may} m_2 / \forall f_i \in \mathcal{F}: m_3(f_i) = \min(m_1(f_i), m_2(f_i)).$

- $m_1, m_2 \in May: m_3 = m_1 \sqcap_{may} m_2 / \forall f_i \in \mathcal{F}: m_3(f_i) = \max(m_1(f_i), m_2(f_i)).$

As before and without details, some elements are not valid, therefore we work on a reduced lattice. we have a Galois insertion:

$$(\wp(D),\subseteq,\bigcup) \stackrel{\alpha_2}{\underset{\gamma_2}{\leftarrow}} (May,\sqsubseteq_{may},\bigsqcup)$$

We define the abstraction function  $\alpha_2$  as:

- $\alpha_2(\phi) = \bot$ .

- $\forall x \in \wp(D) : \alpha_2(x) = m \in May / \forall f_i \in \mathcal{F} : m(f_i)$  = the minimal age of the function  $f_i$  in all concrete cache states.

So,  $\alpha_2(x)(f_i) = \omega$  means that  $f_i$  is not cached, and  $\alpha_2(x)(f_i) = k$  means that  $f_i$  it will be evicted after at most NB - k references that are not in the abstract cache (or are older or the same age as  $f_i$ ).

We define the concretisation function as:

- $\gamma_2(\perp) = \phi$ .

- $\forall m \in May \setminus \{\bot\} : \gamma_2(m) = \{d \in D / \forall f_i \in \mathcal{F} : \text{age of } f_i \text{ in } d \geq m(f_i)\}.$

The access function:  $\widehat{cl'}(m, f_i)$  is done as follows: if  $m(f_k) = \omega$  then it is a miss (**M**) else it is an unclassified reference (**U**). The update function is noted  $\widehat{\Delta'_i}$ .

#### 2.3.3 Collaboration must/may

We can combine these two abstractions with a new connection:

$$(\wp(D),\subseteq,\bigcup) \stackrel{\bar{\alpha}}{\underset{\bar{\gamma}}{\longleftarrow}} (Must \times May,\sqsubseteq,\bigsqcup)$$

Where:

$\forall (m_1, m_2), (m'_1, m'_2) \in (Must \times May) : (m_1, m_2) \sqsubseteq (m'_1, m'_2) \Leftrightarrow m_1 \sqsubseteq_{must} m'_1 \land m_2 \sqsubseteq_{may} m'_2.$

$\forall x \in \wp(D) : \overline{\alpha}(x) = (\alpha_1(x), \alpha_2(x)) \text{ and } \forall (m_1, m_2) \in Must \times May : \overline{\gamma}(m_1, m_2) = \gamma_1(m_1) \cap \gamma_2(m_2).$

$\forall m = (m_1, m_2) \in Must \times May : \bar{\gamma}(m) = \gamma_1(m_1) \cap \gamma_2(m_2)$ . The two analyses cannot contradict each other. So, can we refine  $m_1$  or  $m_2$ ?

**Example:** We take the same cache structure as before; if  $m_1 = (1, \omega)$  and  $m_2 = (1, 0)$  then:  $\gamma_1(m_1) = \{[f_1(0), \phi], [f_1(0), f_2(1)], [f_2(1), f_1(0)], [f_2(0), f_1(1)], [f_1(1), f_2(0)]\}$  and  $\gamma_2(m_2) = \{[f_2(0), f_1(1)], [f_1(1), f_2(0)], [f_2(0), \phi], [\phi, \phi]\}.$ So,  $\gamma_1(m_1) \cap \gamma_2(m_2) = \{[f_2(0), f_1(1)], [f_1(1), f_2(0)]\}$ , therefore we can refine  $m_1$  to  $\alpha_1(\{[f_2(0), f_1(1)], [f_1(1), f_2(0)]\}) = (1, 0).$

One way to use this collaboration without computing the reduced product, is to collaborate the access functions.

**Example:** Let an analysis where the concrete semantics is  $x = \{[f_1(0), \phi]\}$ .  $\gamma_1(\alpha_1(x)) = \{[f_1(0), \phi], [f_1(0), f_2(1)], [f_2(1), f_1(0)]\}$  and  $\gamma_2(\alpha_2(x)) = \{[\phi, \phi], [f_1(0), \phi]\}$ . We have  $cl(\gamma_1(\alpha_1(x)), f_2) = \mathbf{U}$  but  $cl(\bar{\gamma}(\alpha_1(x), \alpha_2(x)), f_2) = \mathbf{M}$ .

For LRU, an access of type **U** is equivalent to an access of type **M** in the update function, therefore the previous observation is useless for the LRU policy but not for a FIFO replacement policy (see §2.5).

### 2.4 Binary Buddy with LRU System

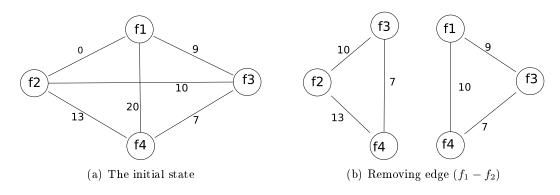

The goal of this section is to illustrate the problem caused by external fragmentation in an LRU system with no constraint on the blocks sizes, and how we can refine the abstract domain to solve the problem. The same refinement approach is followed in the analysis of the next cache management system. Obviously, the non-fixed size blocks will eliminate the problem of internal fragmentation; but in the other side, it is the source of a great amount of external fragmentation. The problem is whether this management system will be predictable or not.

#### 2.4.1 An Imprecise Abstraction

The must-analysis already defined is also correct in this case; correct until the obtaining of the Galois insertion. The problem now is to find the abstraction of the update function. The function  $\widehat{\Delta}_i = \alpha_1 \circ \Delta_i \circ \gamma_1$  is no longer precise essentially when the reference to the function  $f_i$  is a miss.